Apps & Mobile Entwicklung

AMD Epyc Venice: 256 Kerne in 2 nm, DDR5-12800 als MRDIMM über 16 Kanäle

Nachdem AMD einige Informationen zu Venice verraten hat, gehen Details nun weiter in die Tiefe. Mit dabei ist MRDIMM über 16 Kanäle. Die 256 Kerne in neuer Zen-6-Architektur aus TSMCs N2-Fertigung werden zusammen mit neuen IO-Dies im neuen Sockel SP7 und SP8 platziert.

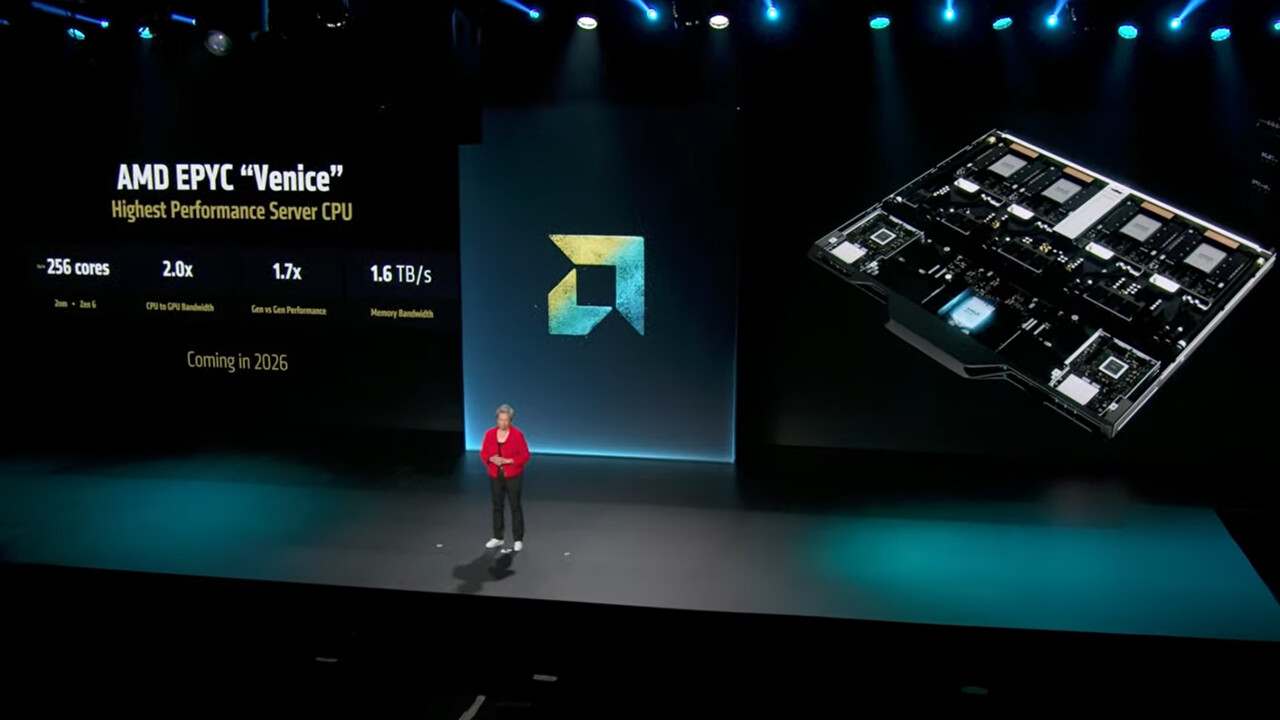

Die grundlegenden Parameter von AMD Venice waren am Abend schnell klar. 256 Kerne im Maximum, dazu eine Verdoppelung der GPU-Bandbreite durch PCI Express 6.0. Einige Fragezeichen bleiben beim Leistungszuwachs, denn hier fehlt die exakte Ausgangsbasis.

Ein 192-Kerner ist heutzutage ein eher niedrig taktender Zen-5c-Chip, klassisch Zen 5 gibt es nur mit 128 Kernen. Ein Drittel mehr Kerne als Zen 5c in neuen CCDs mit neuer Architektur und höherem Takt könnten durchaus in diese Richtung gehen, die AMD mit 1,7-facher Leistung beschreibt. Denn die zur Verfügung stehende TDP erhöht sich für den größeren Sockel SP7 schließlich auch noch, zur Computex 2025 waren bereits Wasserkühlungen für 600 Watt für den Sockel SP7 zu sehen.

Das größte Mysterium am gestrigen Abend war, wie AMD auf die extrem hohe Speicherbandbreite kommt, aktuelle Epycs bieten schließlich nur 600 GB/s. Die Vermutung ging bereits in Richtung zusätzliche Kanäle und höheren Takt, der Schlüssel ist letztlich aber die Verwendung von MRDIMM. Diesen hatte Intel als MCR-DIMM-8800 mit Granite Rapids eingeführt, seit Neuestem aber auch MRDIMM genannt, bei AMD Venice wird dieser auf 12800 MT/s beschleunigt.

Der neue Sockel SP7 wird zudem 16 Speicherkanäle unterstützen, der für Workstation-Aufgaben gedachte kleinere Sockel SP8, Stichwort Threadripper, wird bei 8 Kanälen bleiben – bei gleicher erhöhter Speichergeschwindigkeit. Gegenüber aktuell genutztem DDR5-6400 im Maximum entspricht dies im Sockel SP8 also einer Verdoppelung, im Sockel SP7 gegenüber dem Sockel SP5 kommt noch etwas hinzu, da 16 statt 12 Speicherkanäle verfügbar sind.

In den Fußnoten hatte AMD gestern auch bereits PCIe 6.0 bestätigt, die zusätzlichen neuen Screenshots untermauern dies. Das Schaubild zum Sockel SP7 zeigt dabei die Verwendung von zwei IO-Dies pro Prozessor, zudem sind acht CPU-Dies mit je 32 Kernen auf dem Package zu finden – der Maximalausbau von 256 Kernen. Die Kernanordnung lässt hier aber vermuten, dass es sich um Venice Dense mit Zen 6c handeln dürfte, so wie Turin Dense mit Zen 5c aktuell.

Bei Sockel SP8 sind ebenfalls zwei IO-Dies verbaut, das interessante hier ist, das sogar 192 PCIe-6.0-Lanes im Dual-Sockel-Betrieb zur Verfügung stehen können. Bei der CPU im Bild dürfte es sich um einen 96-Kerner handeln – 8 CCDs mit je 12 Kernen. Die neuen 12-Kern-CCDs hatten sich zuletzt manifestiert, sie dürften auch in vielen anderen Bereichen wie im Desktop zum Einsatz kommen und dort den Schritt von 16 auf 24 Kerne als Maximum bieten. Diese größeren CCDs dürften dann vermutlich auch bei Venice Classic genutzt werden, in der heutzutage bei Turin Classic genutzten Anordnung mit 16 CCDs auf dem Package würde daraus ein 192-Kerner werden. Das ist aber nur eine Vermutung.