Apps & Mobile Entwicklung

Kein Selbstläufer: TSMC N3P kämpft mit Yield, SRAM skaliert auch bei N2 nicht

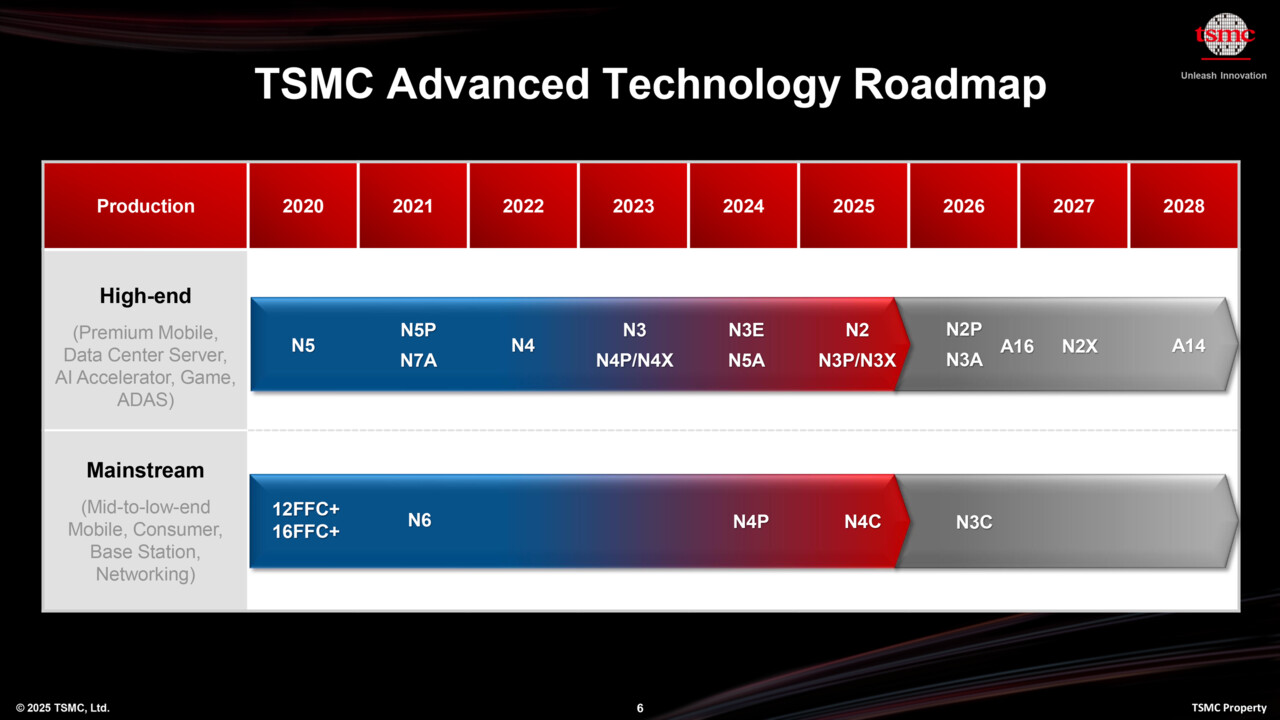

Die Chipfertigung am Rande des Möglichen stellt TSMC vor extreme Herausforderungen. Der N3-Prozess hatte schon einige dieser zu lösen, der erste N3-Prozess war bekanntlich quasi komplett unbrauchbar, erst mit N3B und N3E ging es dann richtig los. Auch N2 skaliert nur bedingt, bei SRAM passiert wohl gar nichts.

SRAM skaliert auch bei TSMC nicht mehr

Das Skalieren von SRAM, also dem geringeren Platzbedarf der SRAM-Zellen, mit stetig fortschrittlicherer Fertigung, gilt bereits seit Jahren als fast unmöglich beziehungsweise sind die Fortschritte nur ganz minimal. Zuletzt keimte die Hoffnung auf, dass TSMCs neuer N2-Prozess mit neuen GAA-Transistoren, also Gate All Around statt FinFETs, hier wieder Bewegung hineinbringen könnte. Doch dem ist nicht so, SRAM skaliert bei N2 laut TSMCs eigenen Aussagen nicht besser als bei den Fertigungsstufen N3 und N5.

Der Verweis im X-Beitrag auf die N3- und N5-Fertigung liefert als Ergebnis die gleiche 0.021 μm² high-density SRAM bit cell, nachzulesen beispielsweise bei IEEE Xplore. Bei N7 lag die Fläche noch bei 0.027μm² und später auch 0.026μm² – Von N7 zu N5 gab es also die letzte Optimierung beim Platzbedarf.

SRAM ist auch in modernen Chips weiterhin ein wichtiger Bestandteil. Die Caches, egal ob Stufe L0, L1, L2, L3 oder L4 werden beispielsweise stetig eher noch größer, damit die CPU- oder GPU-Kerne noch mehr Daten noch näher am Kern halten können, was die Leistung steigert. Die anderen Einheiten rundherum um den SRAM skalieren in der Regel besser, im Gesamtpaket kann dies entsprechend designt werden und trotzdem letztlich eine gewisse Platzersparnis bringen. Dass moderne Chips pauschal letztlich aber kleiner werden, ist nicht abzusehen, vielmehr blähen zusätzliche Features und Ausstattungsmerkmale die Designs eher weiter auf, was die Chips größer und noch teurer macht.

Ausbeute bei N3P entwickle sich nur langsam

TSMCs aktueller N3P-Fertigungsschritt ist dafür gedacht, dass High-Performance-Lösungen noch etwas mehr Leistung bieten können. Er ist direkt dafür ausgelegt, Nvidias Rubin-Chip wird deshalb unter anderem darauf setzen. Dabei bewegt sich TSMC aber so nah am Rand des Möglichen, dass die Ausbeute darunter leidet und sich langsamer zu einem guten Wert entwickle, als geplant.

Wie SemiAnalysis gestern beschrieb, müssen Kunden nun warten oder die Zeit für einen Re-Spin nutzen, der eine höhere Ausbeute verspricht.

The challenge is that N3P does this while pushing interconnect scaling and patterning almost as far as current EUV tools allow. Minimum metal pitches in the low 20s of nanometers, high aspect ratio vias, and tighter optical shrinks all amplify BEOL variability and RC. Issues like via profile control, under-etch, and dielectric damage become first order timing problems. For TSMC, that means more fragile process windows, more sophisticated in-line monitoring, and heavier use of DTCO feedback loops to keep design rules aligned with what the line can print at scale. We currently see a slower than expected improvement in defect density of N3P, which is causing chip designers to either re-spin for yield or to wait in the queue for process improvements.

SemiAnalysis

Unterm Strich kann sich TSMC diese Probleme und Herausforderungen aber leisten. Schon mit dem ersten, problembehafteten N3-Prozess verlor TSMC letztlich eigentlich fast ein Jahr, was aber kaum Relevanz hatte, da es keinen Konkurrenten gab. Die Kundschaft wie Apple drehte Ende 2022 eine „Ehrenrunde“ im N4-Prozess, im Jahr darauf rückten sie zu N3B und später N3E vor. Viele High-End-Chips warten in der Regel ohnehin oft ein Jahr, bis sie zum besten Fertigungsprozess vorrücken, da für größere Chips Anfangs die Ausbeute geringer ist und erst im Verlauf stetig besser wird.