Apps & Mobile Entwicklung

Teures Packaging: CoWoS-Wafer kosten fast so viel wie 12-Zoll-Scheiben mit 7-nm-Chips

Packaging für alle Arten von Chips ist das Thema der letzten und nächsten Jahre. Das bedeutet hohe Preise, aber auch hohe Profite. Die modernsten Produkte von TSMC aus der CoWoS-Familie sind auf den Wafer gerechnet mittlerweile so teuer, wie ein regulär belichteter Wafer mit 7-nm-Chips: rund 10.000 US-Dollar.

1 × CoWoS-Wafer = 5 × UMC-Wafer mit 40-nm-Chips

Es sind Daten, die bedürfen einer Einordnung. Nur drei Firmen weltweit stellen überhaupt Chips in einer 7-nm-Größe her: TSMC, Intel und Samsung. Jeder andere Halbleiterhersteller ist nicht einmal ansatzweise in dieser Region unterwegs, weshalb auch die Preise, die diese Unternehmen für ihre Produkte abrufen können, oft viel geringer ausfallen und sie so auch am großen Boom aktuell nur minimal teilhaben.

UMCs Waferpreis liegt als weltweite Nummer 4 der Chip-Auftragshersteller beispielsweise seit vielen Quartalen auf nahezu identischem Niveau bei knapp 2.000 US-Dollar. Zweidrittel des Umsatzes kommen aber auch aus Produkten in 40 nm und darüber.

CoWoS kann immer mehr

Die nun genannten 10.000 US-Dollar für einen CoWoS-Wafer (womit primär der Interposer gemeint ist) zeigen deshalb, was für gewaltige Unterschiede in der Branche bestehen. CoWoS (Chips on Wafer on Substrate) hatte sich in den letzten Jahren zum Kassenschlager entwickelt. Die gestiegenen Kosten sind vor allem auf die neuen Möglichkeiten zurückzuführen. Denn der Interposer ist nun nicht mehr nur ein passives Element, auf dem Chips gepackt sind, vielmehr bietet er nun verschiedene Features wie eine integrierte Stromversorgung, seit neuestem auch Local Silicon Interconnects (LSI) – das ist das L in CoWoS-L für die aktuellen Nvidia-Chips – und embedded Deep Trench Capacitor (eDTC) für High-Performance-Chips.

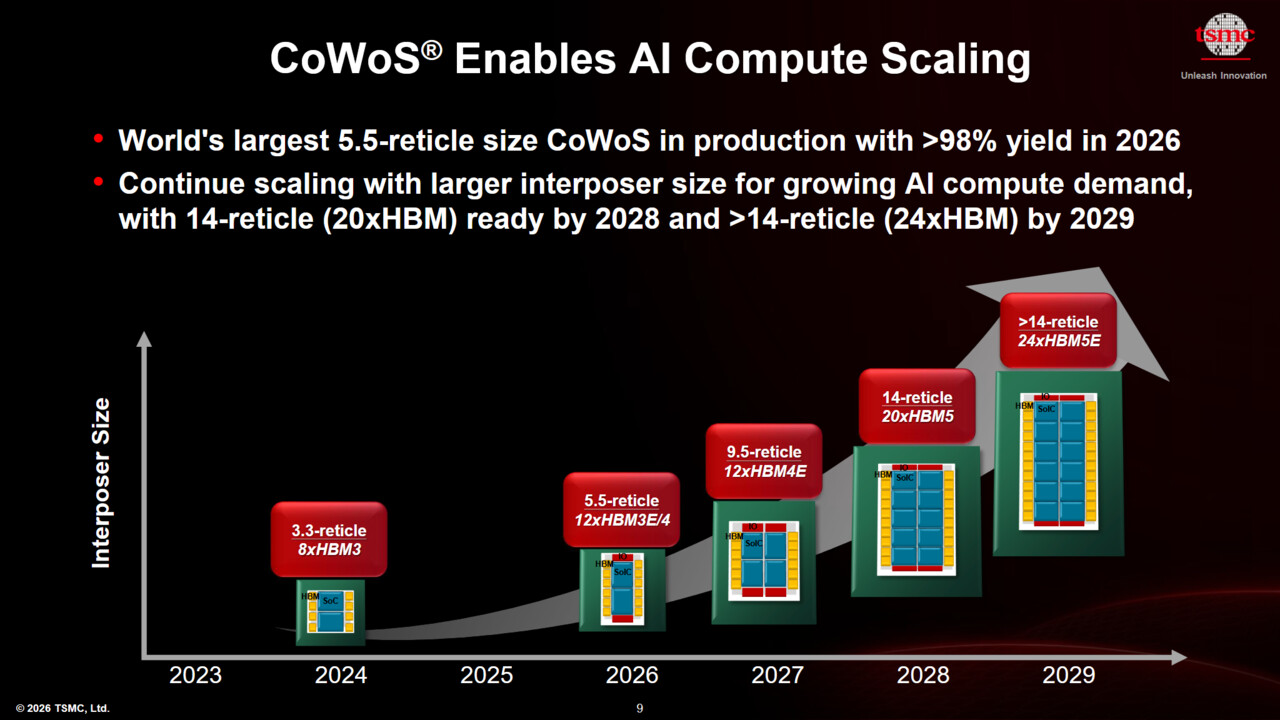

Kein moderner größerer Chip ist deshalb ohne diese Technologie verfügbar. In diesem Jahr werden so primär gepackte Chips in der Größe von 5,5 Reticles gefertigt, laut TSMC mit einer Yield-Rate (Ausbeute) von über 98 Prozent. Hatte TSMC im letzten Jahr die Grenze auf 9,5 Reticles verschoben, wird sie in diesem Jahr noch einmal deutlich weiter nach oben gesetzt. Nicht nur werden Größen von 14 Reticles bereits ab 2028 anvisiert, im Jahr darauf soll das ganze Konstrukt noch einmal größer werden können. Ohne exakte Angaben steht hier deshalb ein wenig als Platzhalter nur „>14 Reticles“, Platz für 20 Prozent mehr Speicher gegenüber dem vorangegangenen Maximalausbau ist aber ebenso gegeben.

Am Ende lässt sich mit dem Gesamtpaket aber viel Geld verdienen. TSMC baut die Packaging-Kapazitäten weiter massiv aus, verdient dazu aber auch jedes Quartal Rekordsummen.