Apps & Mobile Entwicklung

Mit SoIC & CoPoS: TSMC will gestapelte Chips ab 2028 auch aus den USA liefern

SoIC steht für System-on-Integrated-Chips und kommt etwa für die gestapelten Chips beim AMD Ryzen X3D zum Einsatz. Und CoPoS steht für Chip-on-Panel-on-Substrate – das kommende Packaging auf Panel-Level. Ab 2028 wird das Packaging-Werk von TSMC in den USA gebaut, das gemäß neuer Meldungen direkt neben den Fabs stehen wird.

Fab und Packaging gehen Hand in Hand

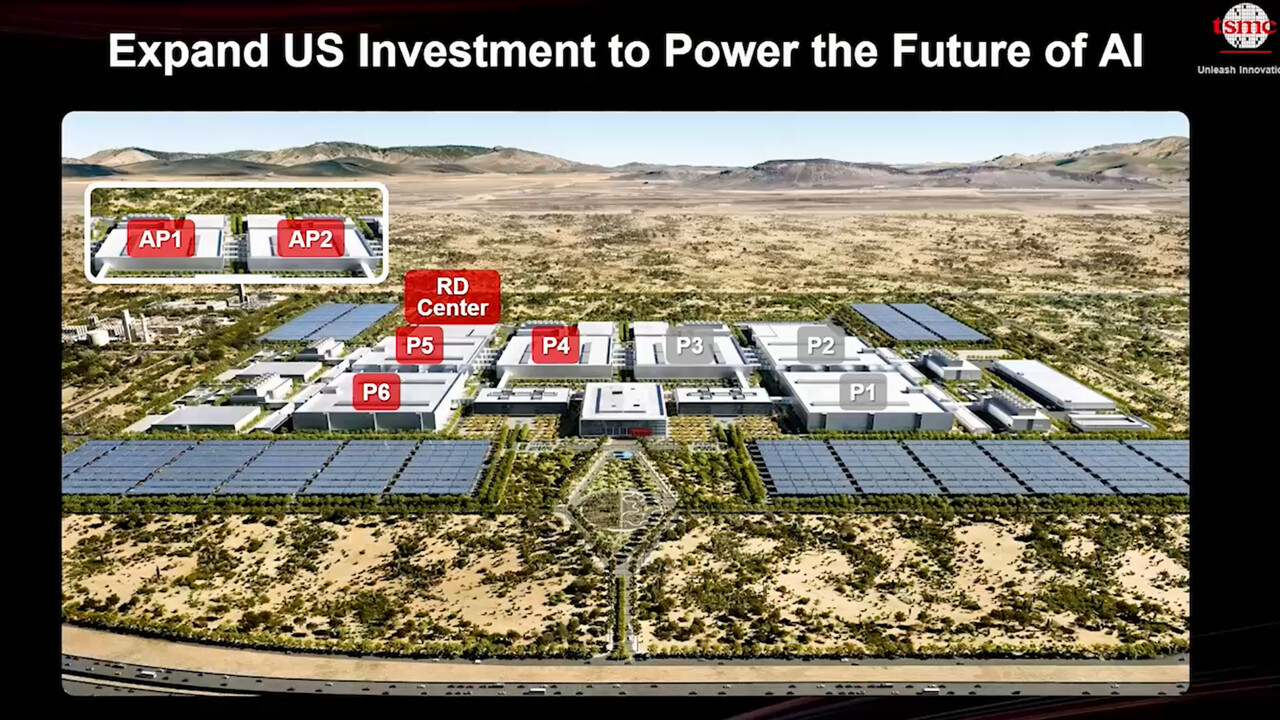

Direkt neben Phase 3 der TSMC-Fab 21 in Arizona könnte die Advanced-Packaging-Einrichtung (AP1) entstehen. In Fab 21 P3 sollen schließlich auch Chips in N2-Fertigung und später eventuell auch in A16 entstehen. Diese Lösungen dürften für ein anschließendes Packaging direkt nebenan prädestiniert sein. Denn in Zukunft wird vermutlich nahezu jeder Chip in irgendeiner Form fortschrittlicher verpackt als nur auf ein Substrat gesetzt, weshalb die Ausbauten überhaupt erst nötig werden.

TSMCs Advanced-Packaging-Einrichtungen in den USA sollen am Ende zwei moderne Gebäude umfassen. Vermutlich wird der zweite Bau zusammen mit der Fab 21 Phase 5 und 6 errichtet, eventuell aber bereits nach der Fab 21 P4 – exakte Zeitpläne gibt es nach außen hin noch nicht. Der Bau von AP1 soll 2028 beginnen.

Passendes Packaging für US-Kundschaft

Für die US-Kunden ist es genau das passende Packaging: SoIC soll in Zukunft nicht nur von AMD genutzt werden, auch Apple wird dies nachgesagt. SoIC wird von AMD aktuell genutzt, um zwei Chips mittels TSVs übereinander zu stapeln – etwa beim X3D-Cache unterhalb des Ryzen-CPU-Dies. Und CoPoS wird ohnehin vermutlich das nächste große Packaging-Verfahren, das CoWoS ablöst respektive ergänzt.

CoPoS steht für „Chips on Panel on Substrate“. Panel bezieht sich in dem Fall auf die Fertigung der passenden und viel größeren Substrate, die nun nicht mehr von einem runden Wafer bezogen werden, sondern einem rechteckigen Panel. Auch in anderen Bereichen soll das Panel-level Packaging (PLP) gegenüber dem Wafer-level Packaging (WLP) in Zukunft an manchen Stellen Vorrang erhalten, es verspricht nämlich eine höhere Wirtschaftlichkeit.

CoWoS, „Chips on Wafer on Substrate“, ist die aktuelle Packaging-Technologie, mit der Nvidia, aber auch AMD und weitere Firmen, beispielsweise GPU-Dies zusammen mit HBM auf einem Package vereinen und so erst den nutzbaren KI-Beschleuniger hervorbringen. Sie dürfte nicht direkt abgelöst werden, aber im High-End-Segment wird CoPoS die Ergänzung sein.

In Medienberichten hieß es zuletzt, TSMC werde im kommenden Jahr eine Pilotlinie für CoPoS errichten. Dort soll die Umsetzung für die Praxis weiter erforscht und entwickelt werden. Ziel sei es, bis Ende 2027 ein brauchbares Programm vorzuweisen, das 2028 durch Partner abgenommen wird. Vor Ende 2028/Anfang 2029 wird es erste Lösungen mit der neuen Packaging-Art vermutlich aber nicht geben – das wiederum passt aber zum Zeitplan der US-Einrichtung, die vor 2030 kaum in Serie produzieren dürfte.