Apps & Mobile Entwicklung

GTC Washington: Nvidia zeigt Vera Rubin Superchip und aktuelle HPC-Roadmap

Ein halbes Jahr nach der GTC 2025 am Firmensitz in San Jose hat Nvidia auf der GTC Washington eine aktuelle High-Performance-Computing-Roadmap gezeigt: Sie bestätigt die im Frühling genannten Termine. Auch einen Vera Rubin Superchip hatte CEO Jensen Huang auf der Bühne zu zeigen.

Feynman schon früher in 2027?

Die Roadmap aus dem März hatte den Rubin-Nachfolger Feynman für 2028 angekündigt. Die neue Roadmap lässt auf den ersten Blick den Schluss zu, dass es schon 2027 so weit sein könnte. Doch auf den zweiten Blick wird klar: Während Nvidia im Frühjahr über die Marktverfügbarkeit sprach, zeigt die neue Vorschau eher, wann Nvidia plant die Architektur fertig entwickelt zu haben. Neue respektive erste handfeste Details zu Feynman hatte Nvidia in Washington noch nicht dabei.

Vera-Rubin-Server „ohne Kabel“

Handfester wurde es im wahrsten Sinne des Wortes beim Vera Rubin Superchip – der dritten Generation der von Nvidia entwickelten Arm-CPU-Dual-GPU-Plattform. Sie liegt inzwischen als Muster der internen Entwicklung vor – passend zum auf der Roadmap genannten Zeitrahmen „2025“. Die Produktion wird aller Voraussicht nach in genau einem Jahr hochgefahren, „möglicherweise etwas früher“, so Huang.

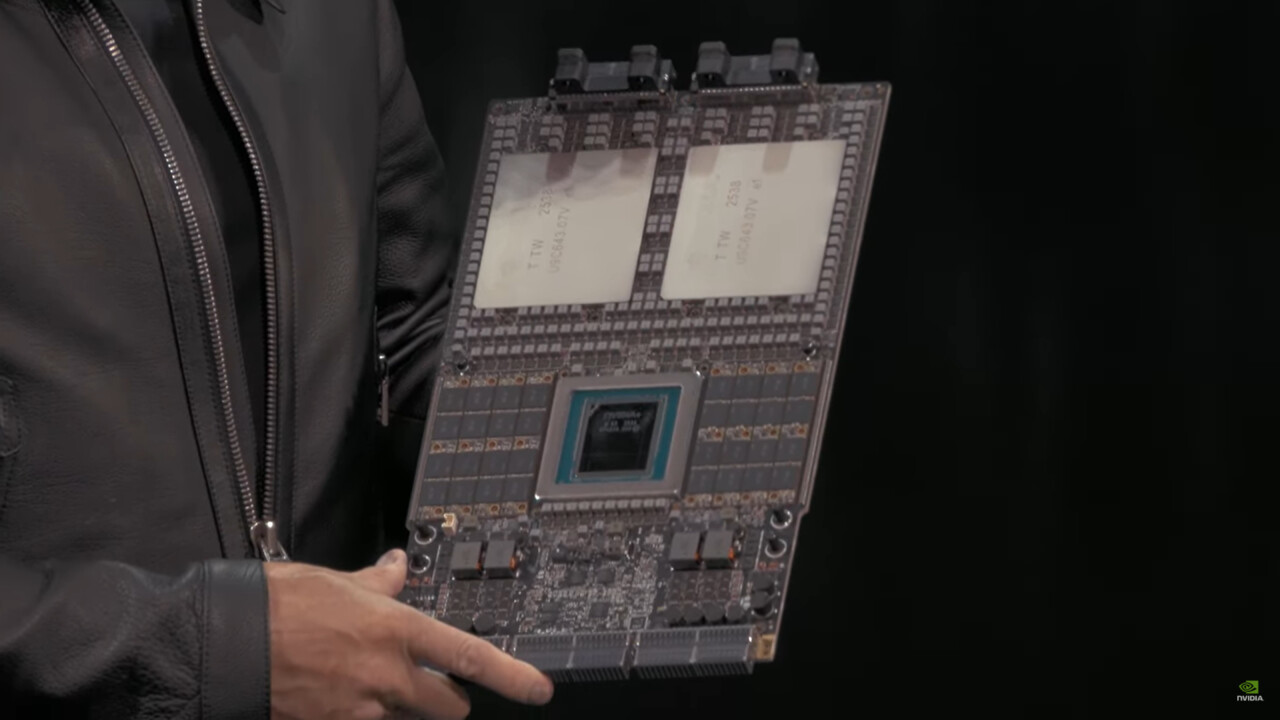

CEO Huang hatte auf der Bühne nicht nur eine solche Platine mit den zwei gigantisch großen Rubin-GPU-Heatspreadern und dem großen Vera-SoC in der Hand, sondern verwies auch auf die so genannten Blades (Server-Einschübe), die in Zukunft ganz ohne intern verlegte Kabel zwischen den einzelnen Komponenten auskommen werden – das, was auf den ersten Blick wie Kabel wirkt, sind die Schläuche der inzwischen zum Standard gehörenden Wasserkühlung. Weitere Dinge werden letztlich primär über Steckverbindungen gelöst, die auch zum Teil den OCP-Standards entsprechen und Partner so leicht zuarbeiten können.

Ein Blick in die Vera-Rubin-(CPX)Blades

Neben dem Vera Rubin Compute Tray (Blade) hatte Huang auch einen Vera Rubin CPX Compute Tray auf der Bühne zu zeigen. Rubin CPX hatte der Hersteller bereits im Sommer vorgestellt.

Rubin CPX entspricht wahrscheinlich einem halben Rubin-Chip (1 Retikel) und ist auf brachiale Rohleistung für einen hohen Inferencing-Durchsatz ausgelegt, vor allem für den FP4-Bereich. Ein einzelner Chip bietet 30 PetaFLOPS FP4-Leistung und setzt wie Rubin eine Flüssigkeitskühlung voraus.

Im bekannten Oberon-Rack, das bei Blackwell (Ultra) und Rubin zum Einsatz kommt, bevor das Kyber-Rack ab Rubin Ultra übernimmt, soll Rubin CPX vor allem „million-token coding and generative video applications“ abwickeln, entsprechend verfügt Rubin CPX auch über jeweils vier Video-Encoder und -Decoder.

Für das Einsatzgebiet von Rubin CPX braucht es darüber hinaus keinen teuren Speicher und entsprechendes Interface im Chip, denn anstelle von HBM4, den Nvidia ab Rubin mit acht Stacks vorsieht, gibt es hier nur GDDR7 in einer Größe von 128 GB – die Menge und Bandbreite liegt entsprechend massiv unter dem klassischen Rubin-Chip (288 GB HBM3e).