Apps & Mobile Entwicklung

NAND-Flash von Kioxia/SanDisk: BiCS9 ist ein Hybrid aus alter und neuer Technik

Das CBA-Herstellungsverfahren mit Logik und Speicherzellen auf verschiedenen Wafern eröffnet Kioxia und SanDisk neue Möglichkeiten. Und so gibt es zwischen den Generationen BiCS8 und BiCS10 den Zwischenschritt BiCS9, der aber sogar bis auf BiCS5 zurückgeht. Verwirrend? Hier kommt die Aufklärung.

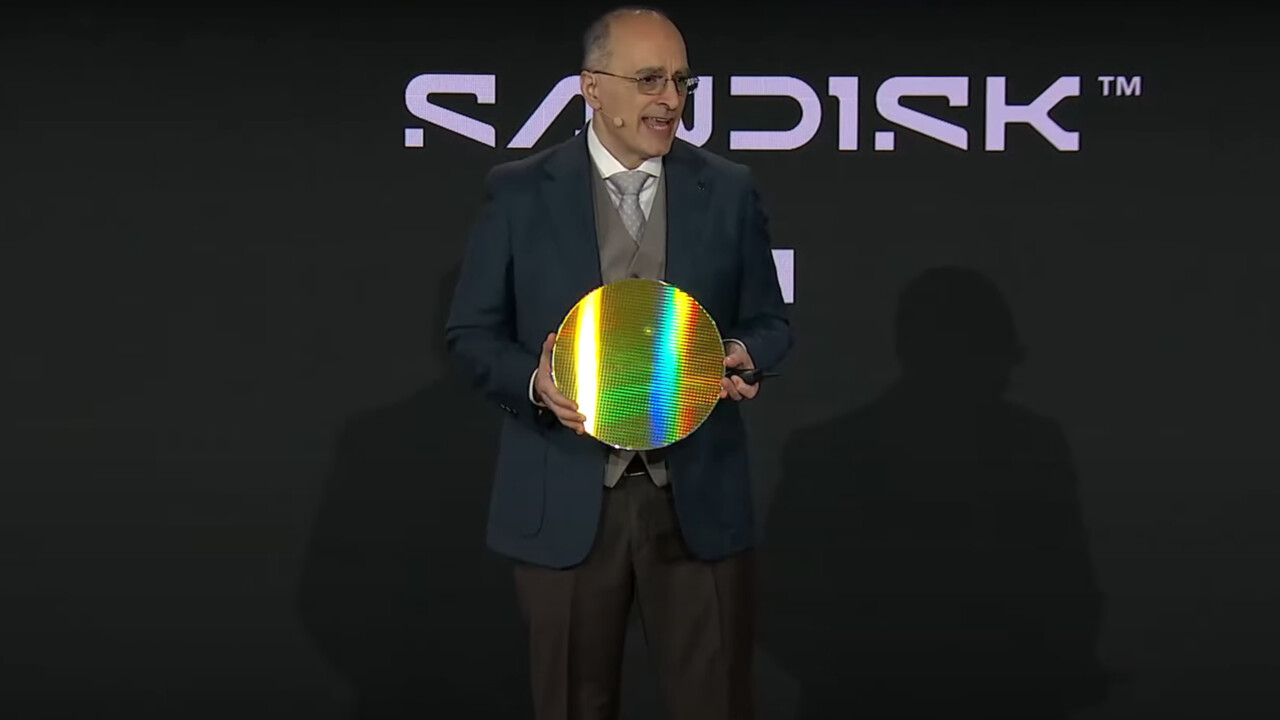

Kioxia stellt BiCS9-TLC-Flash vor

Zunächst einmal zur heutigen Vorstellung von Kioxia, dem japanischen NAND-Flash-Hersteller, der gemeinsam mit SanDisk 3D-NAND entwickelt und produziert: Kioxia lässt verlauten, dass die ersten TLC-Speicherchips der 9. Generation (BiCS9) bemustert werden. Die Serienfertigung soll noch im Laufe des Geschäftsjahres 2025 erfolgen, das allerdings erst am 31. März 2026 endet. Somit kann es also noch bis zum nächsten Kalenderjahr dauern.

Die TLC-Speicherchips mit 3 Bit pro Zelle besitzen eine Speicherkapazität von 512 Gbit pro Die. Das ist nur halb so viel wie inzwischen für TLC-NAND üblich und nur ein Viertel dessen, was die BiCS8-Generation als QLC-Variante liefert.

Kioxia verspricht eine gegenüber TLC-Flash mit 512 Gbit aus der sechsten Generation (BiCS6) um 61 Prozent verbesserte Schreibleistung und ein 12 Prozent schnelleres Lesen. Außerdem soll die Energieeffizienz beim Schreiben um 36 Prozent und beim Lesen um 27 Prozent besser ausfallen.

- Write performance: 61% improvement

- Read performance: 12% improvement

- Power efficiency: enhanced by 36% during write operations and 27% during read operations

- Data transfer speed: the Toggle DDR6.0 interface enables high-speed 3.6Gb/s(5) NAND interface performance

- Bit density: increased by 8% through advancements in planar scaling

Kioxia

Verwirrend wird es dann bei den weiteren Angaben, denn der BiCS9-Flash soll einerseits in einem 112-Layer-Verfahren auf Basis des älteren BiCS5 entwickelt worden sein, andererseits verfüge er über eine moderne Toggle-DDR6.0-Schnittstelle mit 3.600 MT/s und könne sogar unter Idealbedingungen 4.800 MT/s erreichen.

Des Rätsels Lösung: CBA

Die Auflösung dieser Diskrepanz liegt in dem seit BiCS8 eingeführten Herstellungsprinzip „CMOS directly Bonded to Array“ (CBA). Wie es zuerst beim chinesischen Hersteller YMTC geschah, werden Logik und Zellen jeweils auf eigenen Wafern gefertigt und anschließend verbunden. Das grundlegende Verfahren nennt sich Waferbonden. In diesem Fall werden Chip-Logik (I/O) und Speicherbereich zunächst getrennt voneinander auf separaten Wafern gefertigt und erst später zu einem Speicherchip vereint. Obwohl somit zwei Wafer benötigt werden, sollen die Kosten insgesamt nicht steigen, da sich auf diesem Weg die Speicherdichte so weit optimieren lasse, dass sich der zusätzliche Wafer lohne, hieß es bei YMTC.

Kioxia und SanDisk nutzen das Prinzip jetzt, um ein älteres, aber kostengünstiges Speicher-Design (BiCS5, 112 Layer) mit einem modernen I/O-Paket samt hoher Leistung zu kombinieren. Daraus entsteht BiCS9 als Abzweig der traditionellen Roadmap. Es handelt sich praktisch um ein Hybrid-Design aus alter und neuer Architektur.

Während beim kommenden BiCS10 primär die Erhöhung der Flächendichte im Fokus steht, die durch die (teure) Anhebung auf 332 Layer erreicht wird, soll BiCS9 primär die Herstellungskosten senken, dank eines neuen I/O-Bereichs aber auch mehr Leistung bieten.

Verwirrung komplett: BiCS9 kann auch BiCS8 enthalten

Eine Fußnote sorgt dann aber erneut für Verwirrung: Kioxia schreibt dort, dass BiCS9 je nach „Modell“ entweder 112-Layer-Technik (BiCS5) oder 218-Layer-Technik (BiCS8) enthalten kann.

- 9th generation BiCS FLASH™ products: these achieve high performance at reduced production cost by leveraging CBA (CMOS directly Bonded to Array) technology(2), which integrates existing memory cell technologies(3) with the latest CMOS technology.

- 10th generation BiCS FLASH™ products: these incorporate an expansion in the number of memory layers to meet the expected future demand for larger-capacity, high-performance solutions.

(2) Technology wherein each CMOS wafer and cell array wafer are manufactured separately in their optimized condition and then bonded together.

(3) A 112-layer 5th generation BiCS FLASH™ and a 218-layer 8th generation BiCS FLASH™ technologies. The new lineup of 9th generation BiCS FLASH™ products will incorporate one of these, depending on the model.

Kioxia