Apps & Mobile Entwicklung

Intel Panther Lake: erste Details zu „Core Ultra 300“

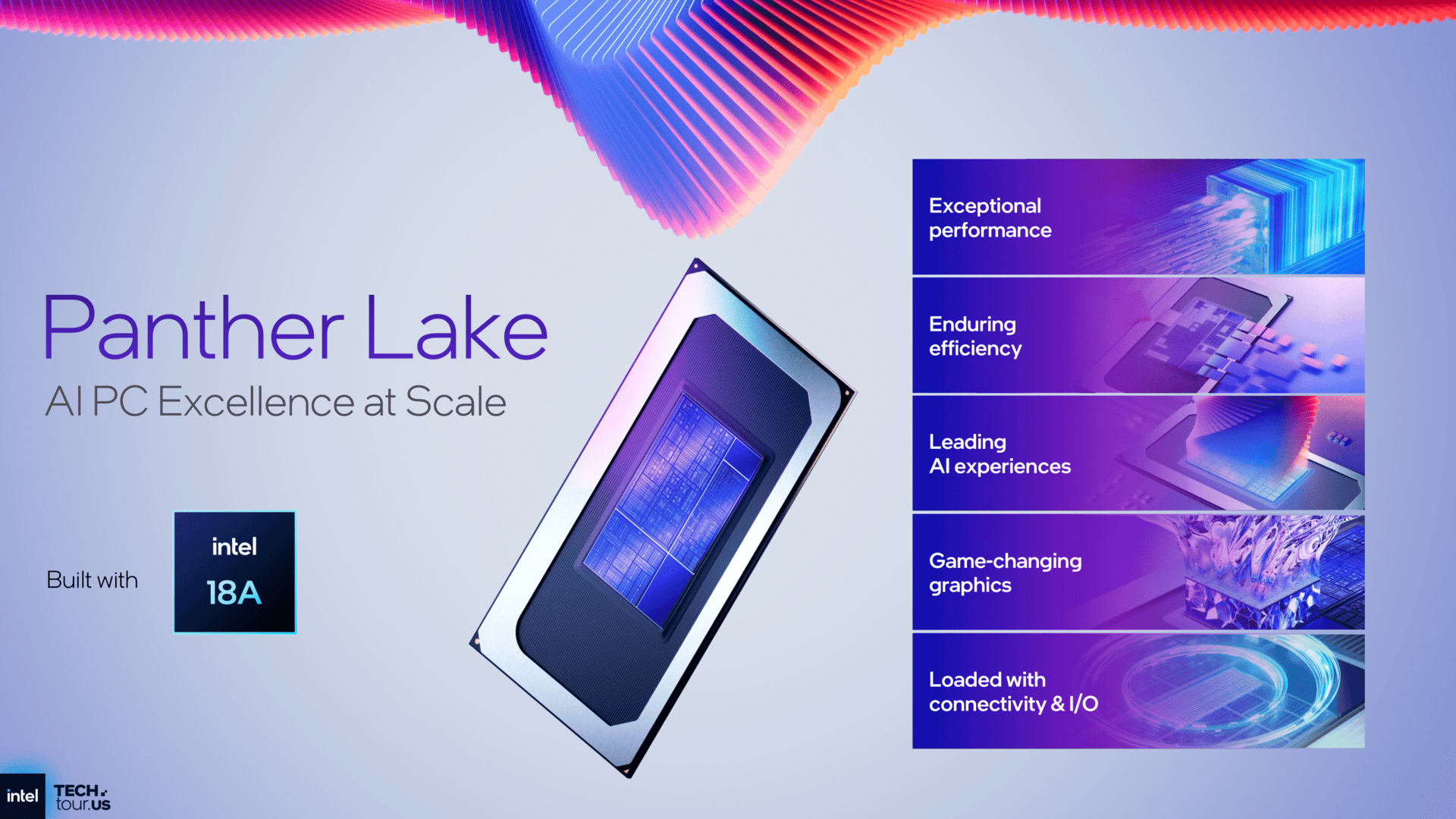

Intel enthüllt Panther Lake, die Basis der Next-Gen-CPUs, die vermutlich „Core Ultra 300“ heißen werden. ComputerBase fasst die Entwicklungen beim Chiplet-Ansatz, den CPU-Kernen, der iGPU sowie der NPU zusammen und erklärt, warum der Chip nun eher wie eine Arm-(Smartphone-)Lösung aussieht. Erste Leistungsaussagen gibt es auch.

Intel Panther Lake alias „Core Ultra 300“

Was jetzt bekannt ist und was nicht

Intel hat Panther Lake offiziell enthüllt. D.h. die technischen Details der Next-Gen-Intel-CPUs, die nur für das mobile und Edge-Embedded-Segment in den Markt gebracht werden, sind bekannt. Die Architektur wird aller Voraussicht nach als „Core Ultra 300“ in den Handel kommen, bestätigt hat Intel das aber noch nicht. Auch konkrete Modelle oder Angaben zu TDP und Taktraten fehlen noch. Das alles dürfte zur CES 2026 im Januar folgen.

Was Intel heute enthüllt, ist die Technik hinter Panther Lake, die mit einem klaren Fokus auf den mobilen Einsatzzweck entwickelt wurde. Sie nimmt Anleihen an Intel Lunar Lake und Intel Arrow Lake-H, aktuell im Handel als Intel Core Ultra 200V und 200H. Auf dieser Basis soll Panther Lake die erste Wahl im x86-Notebook des Jahres 2026 darstellen. Gesockelt für Desktop-PCs erscheint Panther Lake nicht.

Intel Panther Lake nutzt Intel 18A

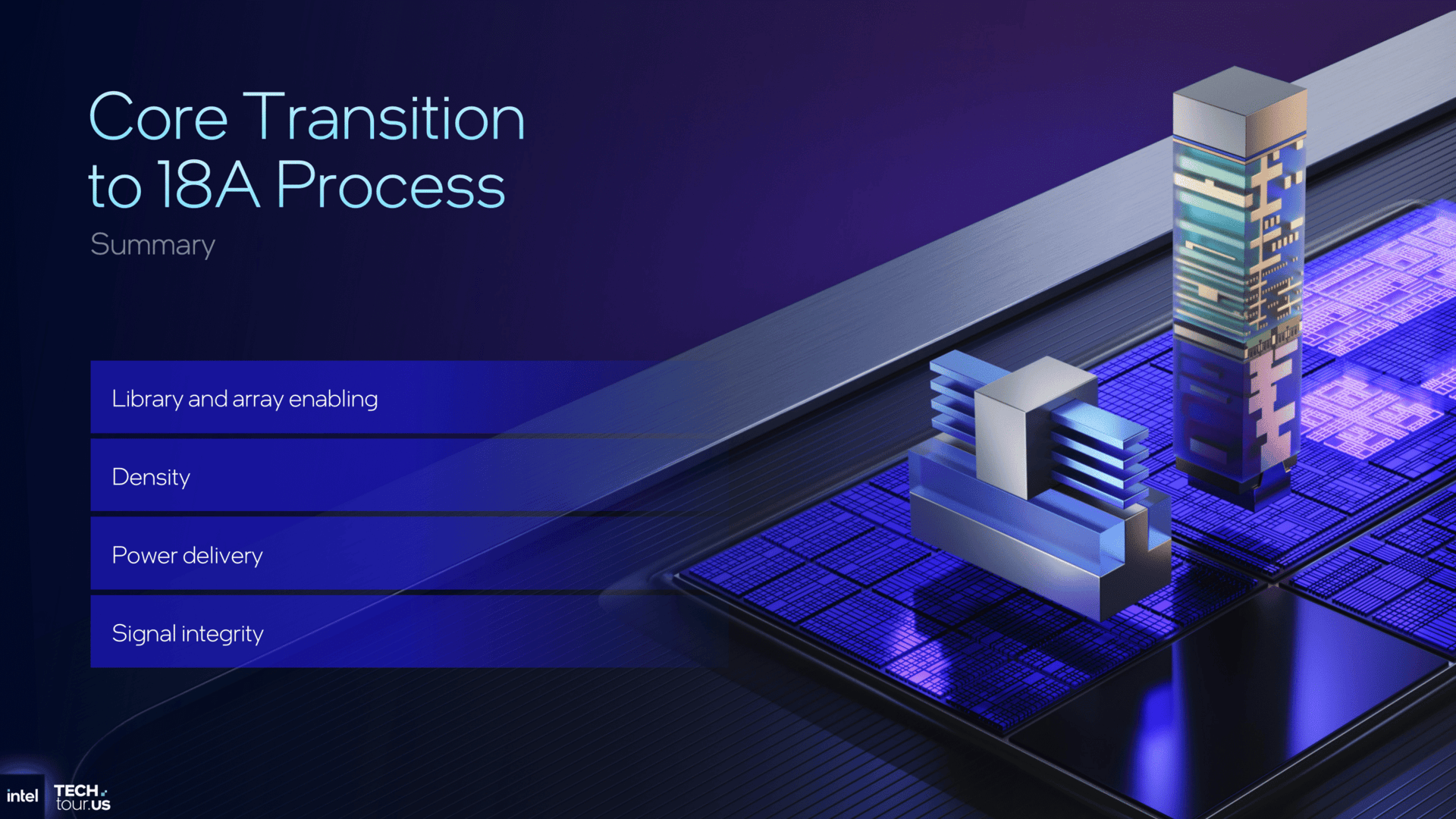

Intel Panther Lake ist dabei der erste Prozessor, der auf einen CPU-Die setzt, der in eigenen Fabriken in der Fertigungsstufe Intel 18A produziert wird – zuletzt kamen auch die CPU-Dies von TSMC.

Viele Jahre hat Intel daraufhin gearbeitet, nun betonen der Hersteller bei jeder passenden Gelegenheit, dass der aktuell beste Fertigungsprozess der Welt in Serienproduktion direkt aus den USA kommt. Dies ist durchaus ein Erfolg und auch deutlich früher als TSMCs konkurrierende N2-Lösung, wenngleich die finale Begutachtung des Prozesses noch nicht möglich ist. Denn Taktraten, Samples und mehr folgen erst in einigen Wochen, der große Start erfolgt nämlich erst zur CES 2026 Anfang Januar.

Parallel zum Panther-Lake-Announcement konnte ComputerBase in Arizona die Fab 52 besuchen:

- Intel 18A läuft an: ComputerBase war in den Reinräumen von Intels Fab 52

Intel Panther Lake in 10 Stichpunkten

- Klassisches System on a Chip (SoC), kein DRAM auf dem Package mehr (wie Intel Lunar Lake)

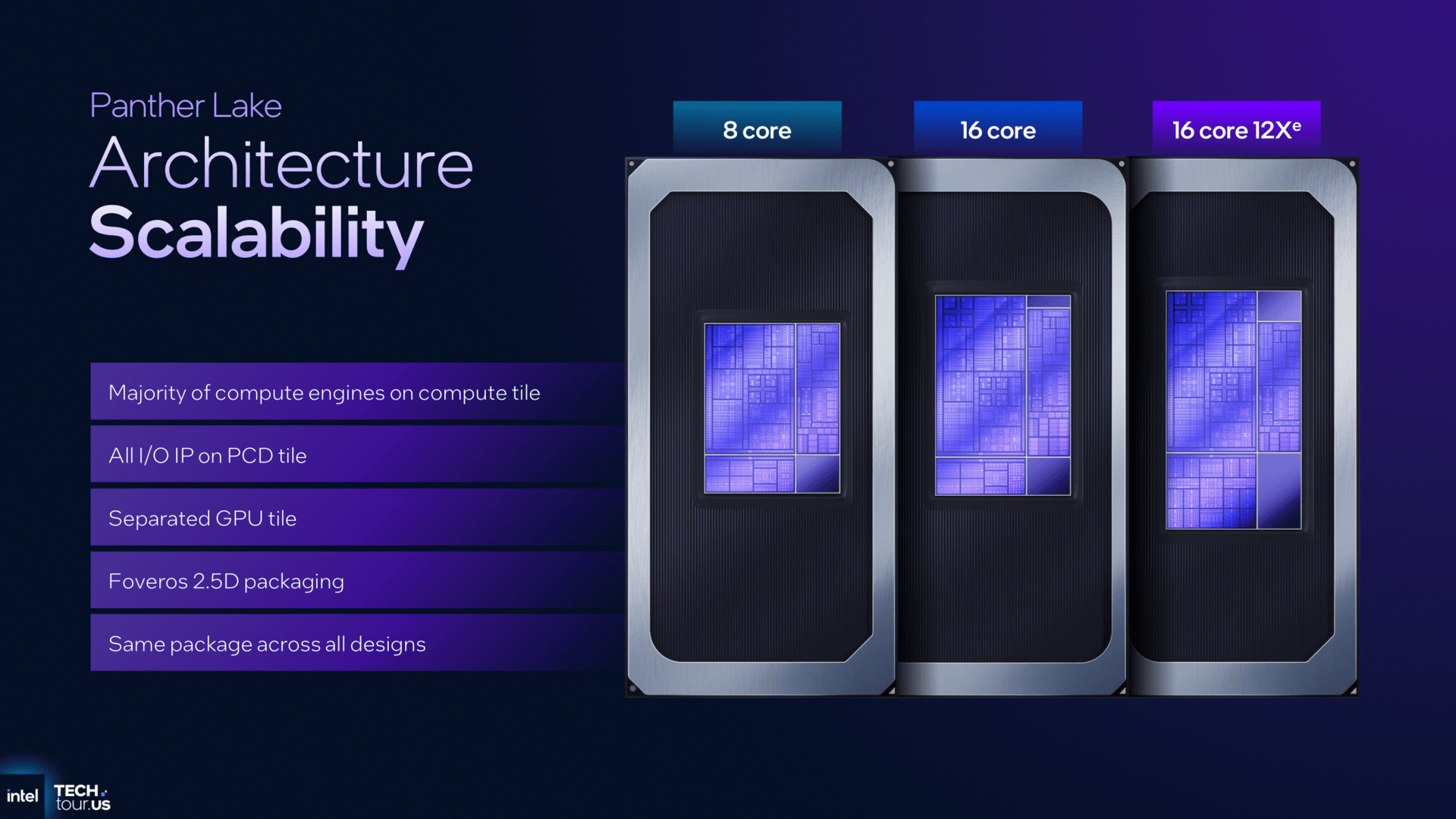

- Baukastensystem aus zwei CPU-Tiles, zwei GPU-Tiles und einem (anpassbaren) I/O-Tile

- LPE-Cores, Speichercontroller und NPU liegen wieder im CPU-Tile

- Fertigung der zwei CPU-Tiles in Intel 18A, TSMC liefert eine von zwei GPU-Tiles und den I/O-Tile

- 16 Kerne: 4 Performance- (P-Cores), 8 Efficiency Kerne (E-Cores) und 4 Low Power Island Cores (LPE)

- P-Cores: Cougar Cove, ungenannter IPC-Zuwachs vs. Lion Cove (Core Ultra 200)

- E-Cores: Darkmont, ungenannter IPC-Zuwachs, im Low-Power-Bereich stärker als Raptor Cove (Core i-13000/14000)

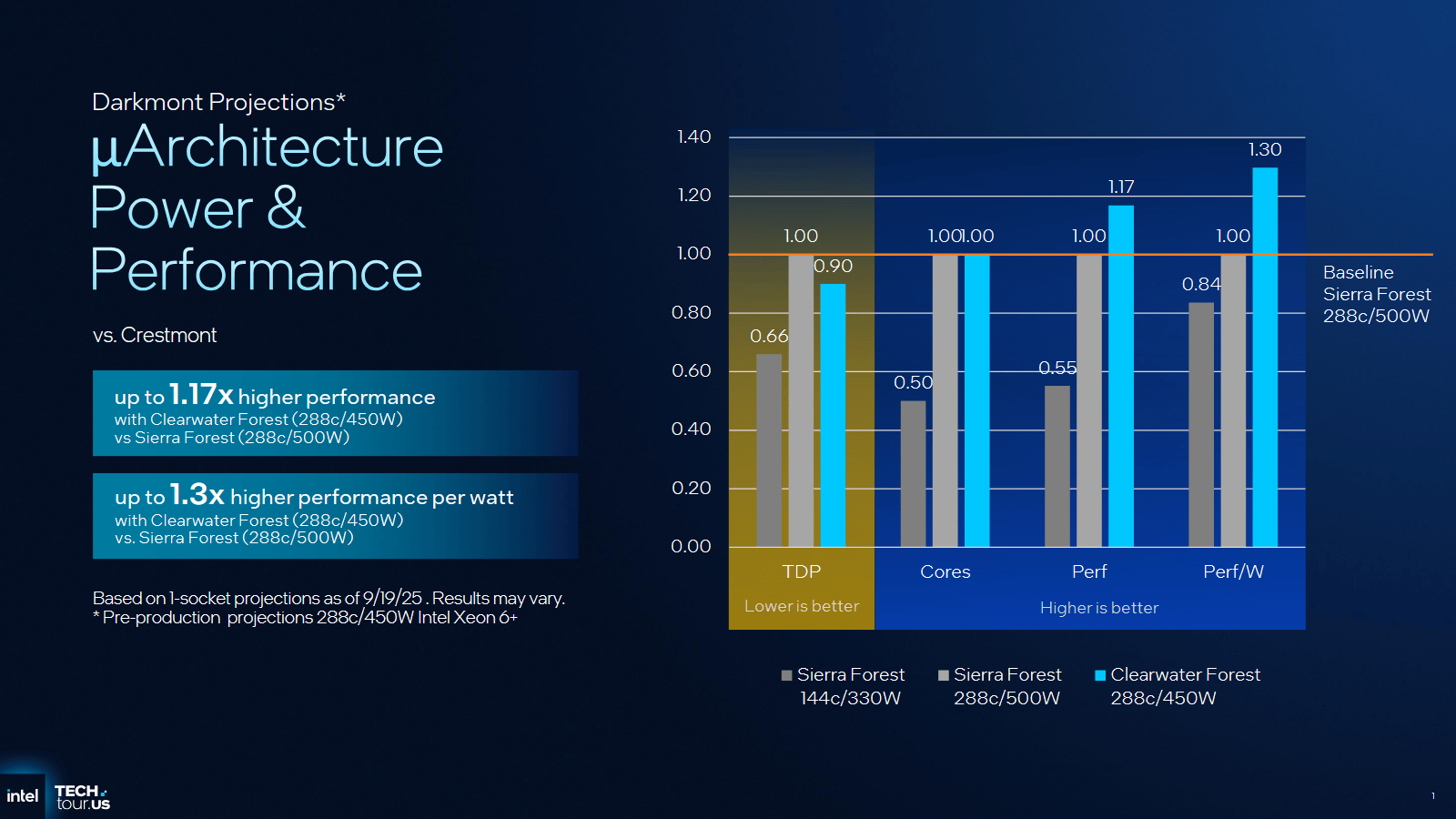

- Die E-Kerne wird auch Intel Clearwater Forest im Server nutzen, dort +17% IPC vs. Crestmont in Intel Sierra Forest

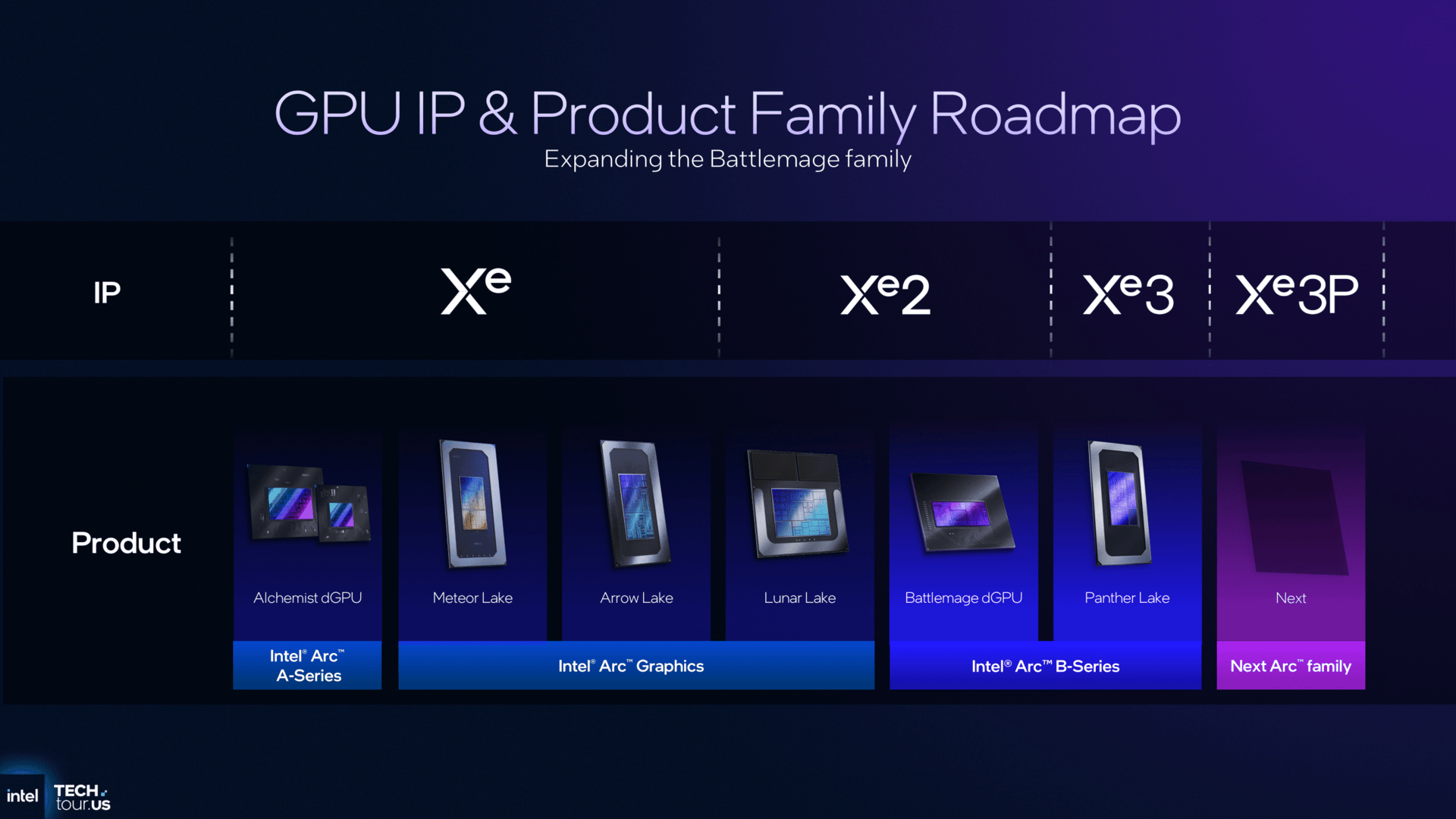

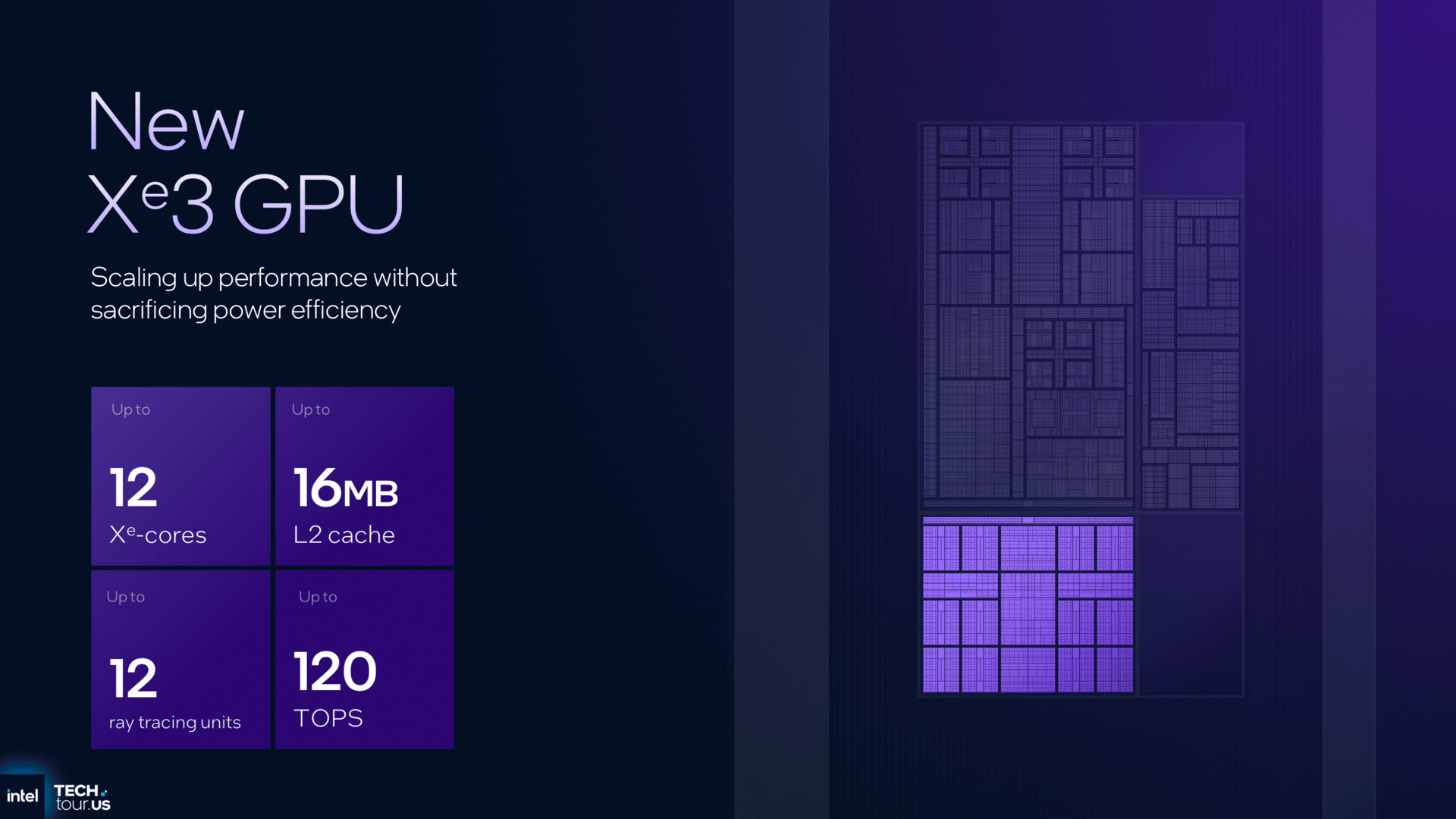

- iGPU: Premiere für Xe3 (kommt auch in Celestial zum Einsatz)

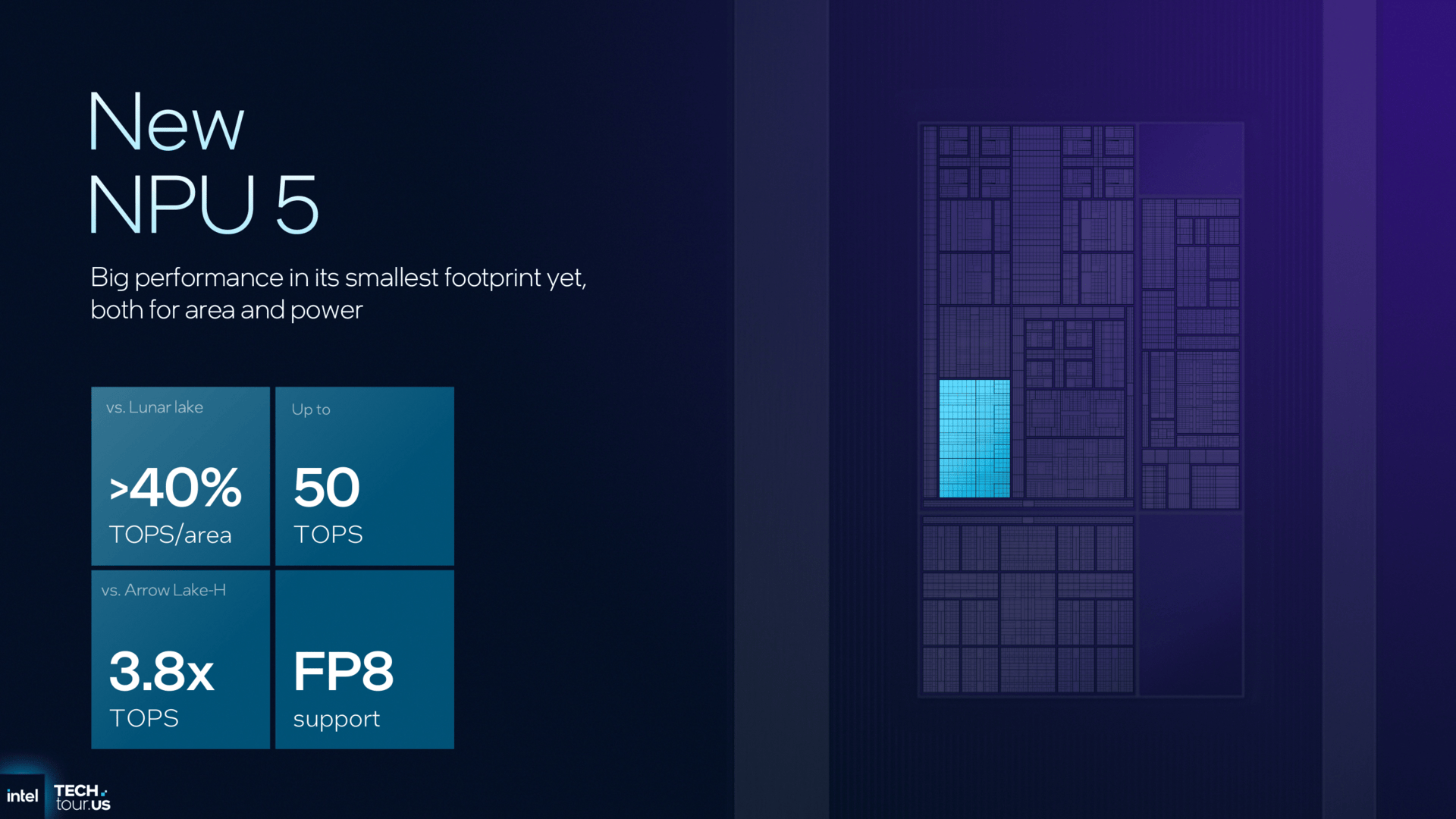

- NPU mit 50 TOPS für Windows Copilot+

Intel Panther Lake im Detail

Drei Chip-Tiles von Intel und TSMC

Panther Lake setzt wie die letzten Intel-Prozessoren auf ein Design, welches aus mehreren Chips, oft auch Tiles genannt, besteht. Konkret sind es drei Tiles, denn den SoC-Tile gibt es nicht mehr. Er enthielt zuletzt unter anderem den Speichercontroller, LPE-Cores und die NPU. Das alles hat Intel bei Panther Lake wieder in den CPU-Tile gepackt. Damit bleiben:

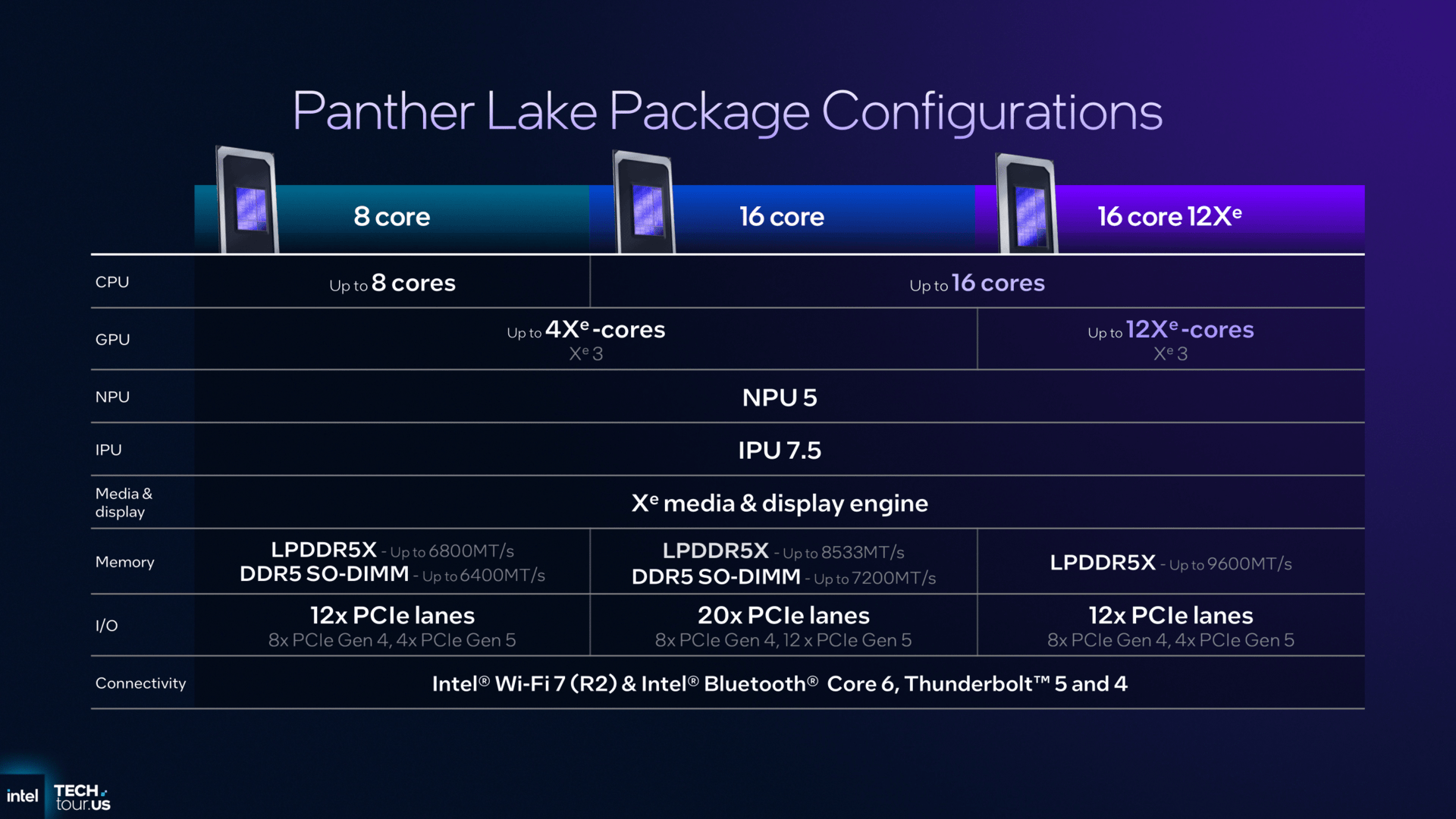

Jeder dieser Tiles liegt in zwei Varianten vor: Zwei CPU-Tiles, zwei GPU-Tiles und zwei I/O-Tiles, wobei es sich beim I/O-Tile um einen physischen Chip handelt, der in zwei Varianten konfiguriert wird. Diese können „beliebig“ miteinander kombiniert werden und ergeben so verschiedene Produkte für ein jeweils anderes Marktsegment.

Der große Tag: Intel 18A ist da!

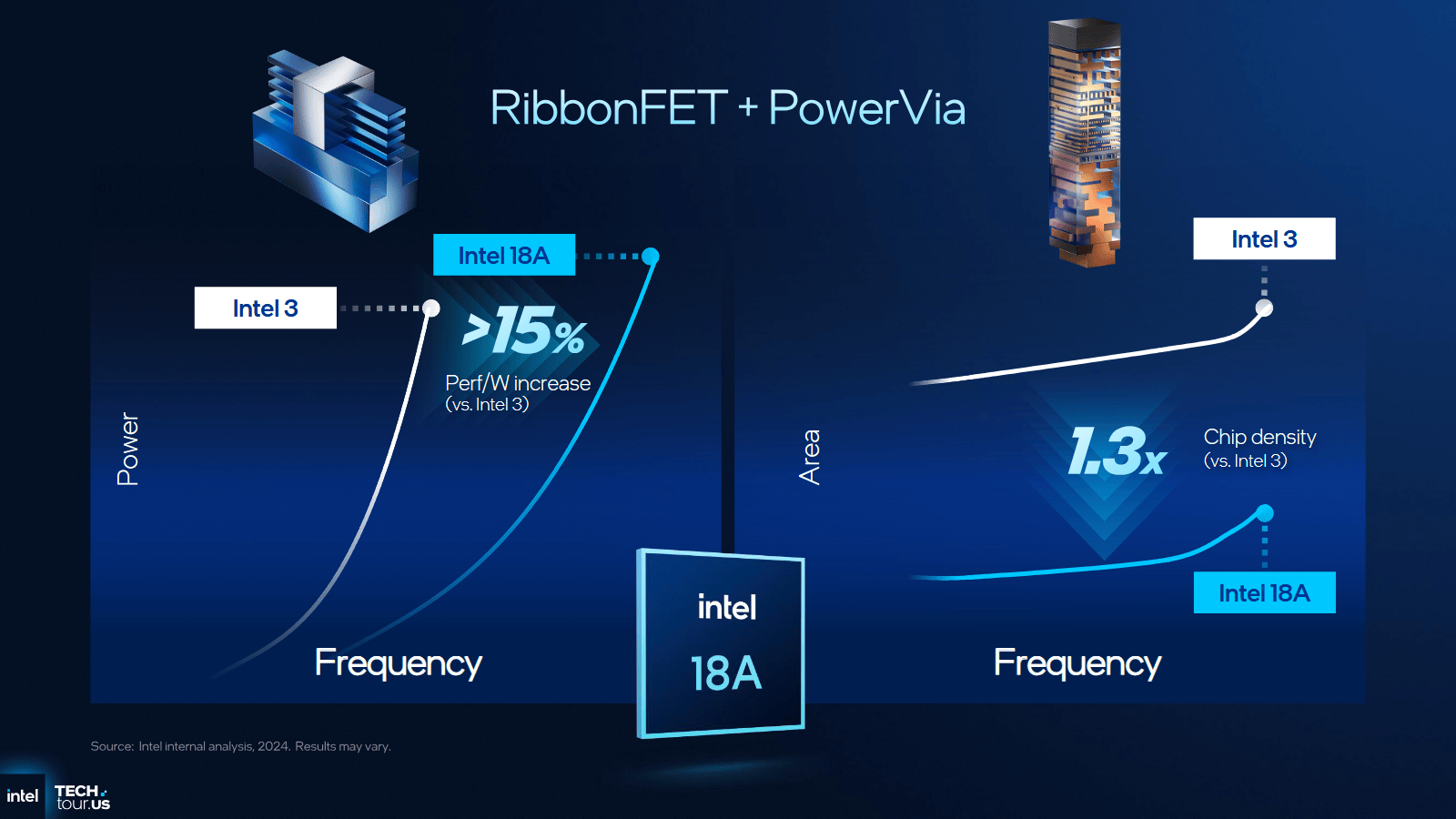

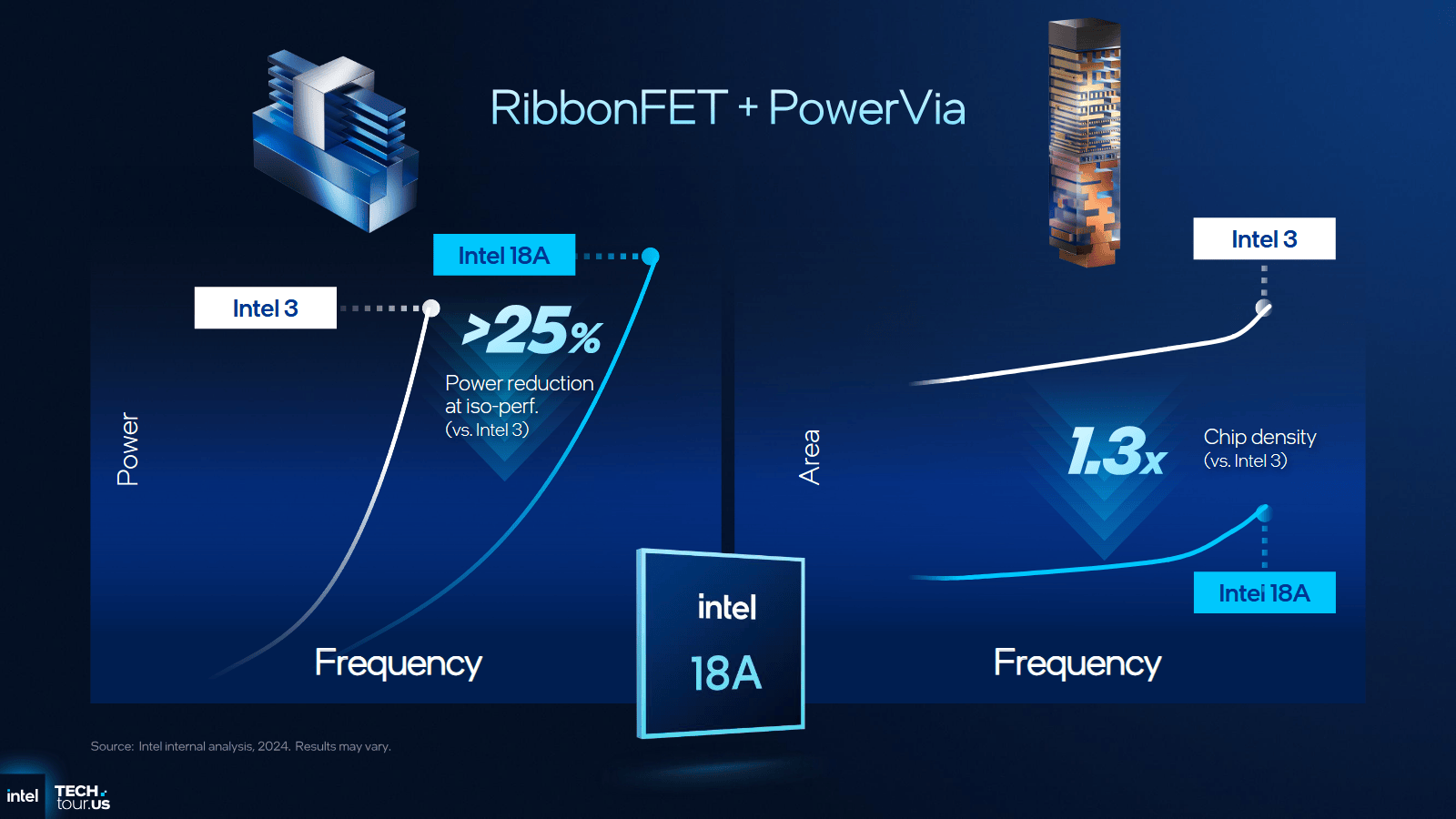

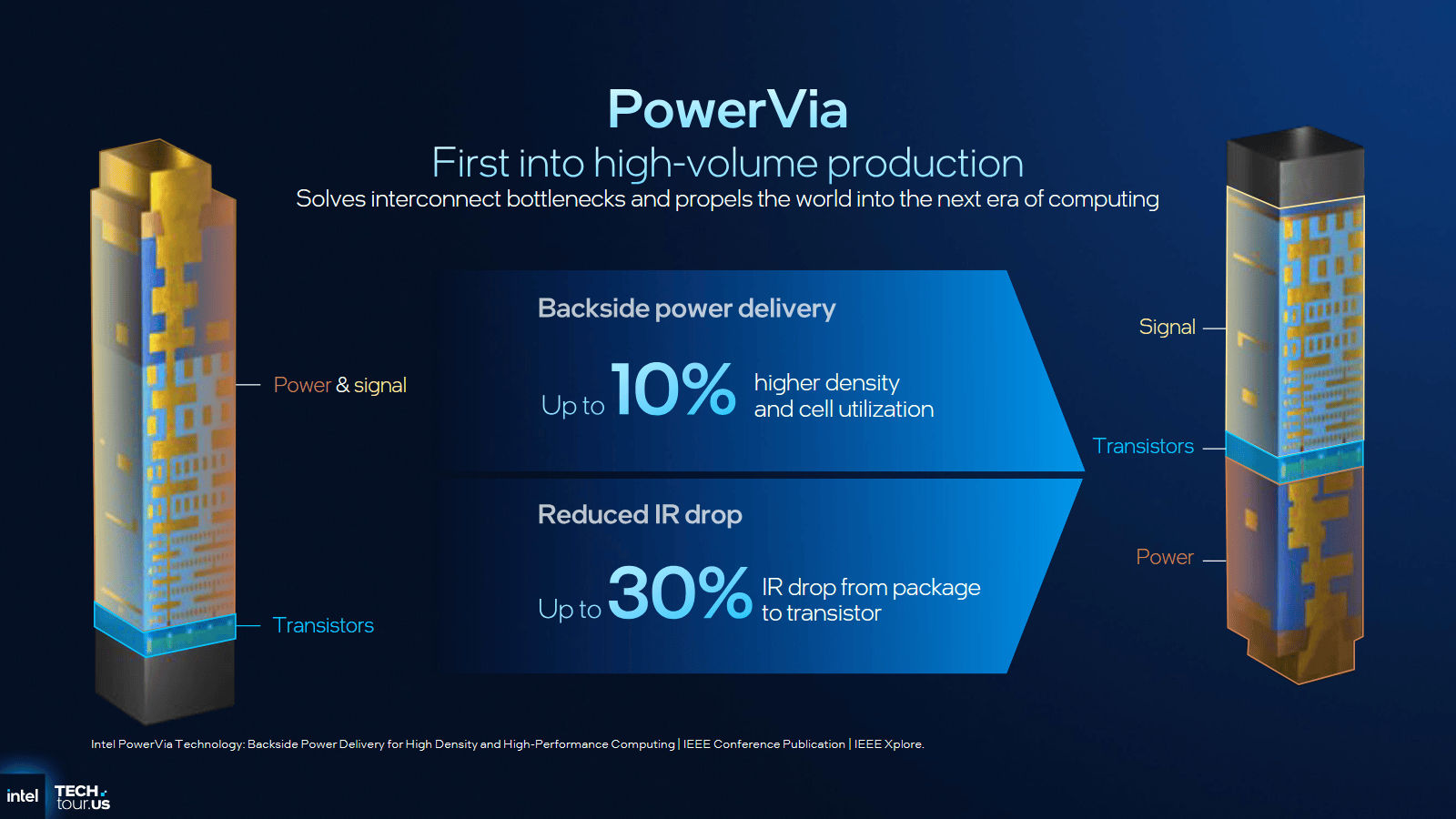

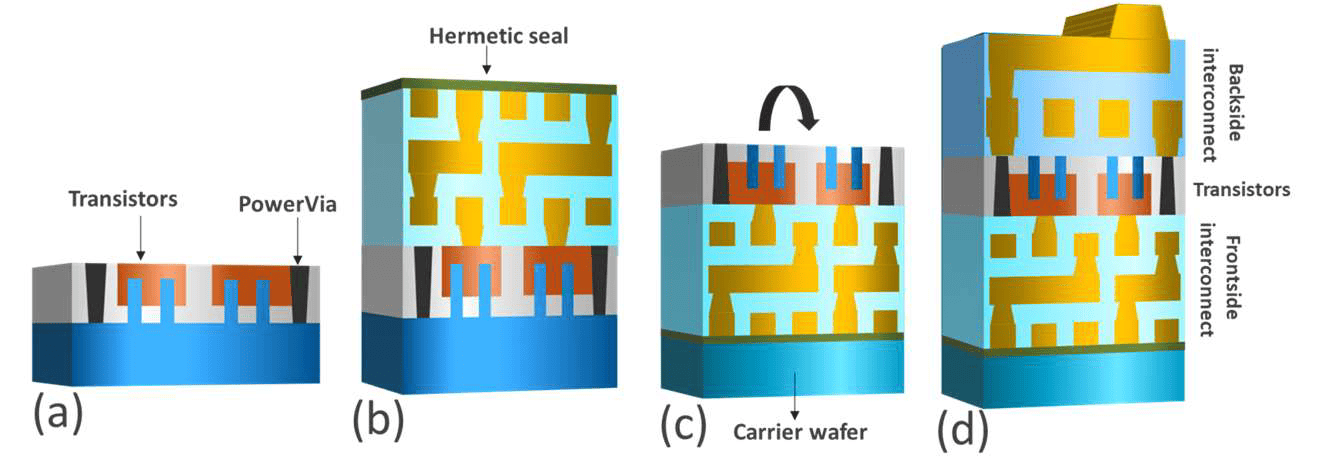

Intel fertigt stets die CPU-Kerne, egal es nun die Konfiguration 4+0+4 oder 4+8+4 ist. Neu ist hierbei natürlich der Prozess, es wird Intel 18A genutzt. Dieser nutzt nicht nur erstmals Gate-All-Around-Transistoren (GAA FET), sondern auch die rückseitige Stromversorgung Backside Power Delivery, bei Intel auch PowerVia genannt. Das Komplettpaket soll vor allem der Effizienz förderlich sein, ist für den Start eines Notebook-Chips also prädestiniert. Mehr Details zu Intel 18A gibt es im separaten Bericht:

- Intel 18A läuft: ComputerBase war in den Reinräumen von Intels Fab 52

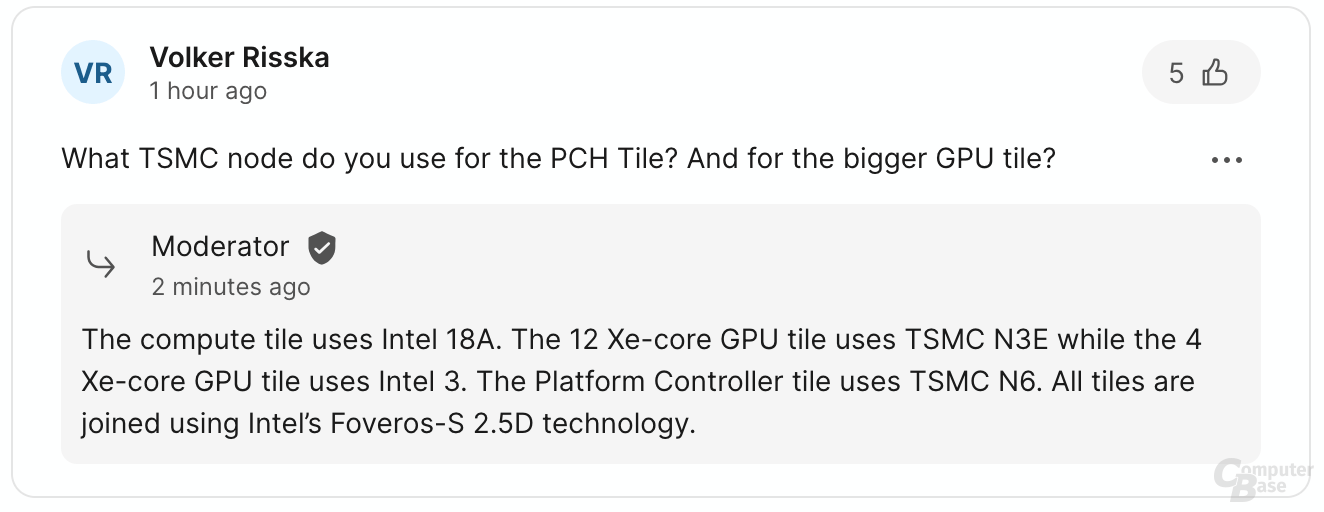

TSMC bleibt mit an Bord

Auch der GPU-Tile wird in der kleinen Konfiguration mit 4 Xe-Cores in Intel 3 gefertigt, in der großen Lösung mit 12 Xe-Cores bleibt es hingegen wie zuletzt bei TSMC N3E. Der I/O-Tile kommt von TSMC und stammt dort aus der inzwischen sehr günstigen N6-Produktion. All diese Angaben wurden von Intel auf Nachfrage von ComputerBase bestätigt.

Dass Intel beim großen GPU-Tile bei TSMC bleibt, hat etwas mit der Performance, der Kapazität und auch dem Timing zu tun. Den kleineren GPU-Tile zu fertigen sei in Intel 3 möglich, der größere fräße jedoch so viele Kapazitäten, die Intel aktuell kaum aufbringen kann. Denn Intel 3 wird für die aktuellen Server-Prozessoren Intel Granite Ridge voll in Beschlag genommen, auch der neue Base-Tile für die E-Core-Server-CPU Intel Clearwater Forest stammt aus Intel 3. TSMCs N3E-Fertigung ist nun Jahre lang erprobt, das Komplettpaket aus zeitlicher Verfügbarkeit, Kapazität und auch gewünschter Leistung dürfte hier einfach das Bessere sein. Mit dem kleinen Tile holt Intel die iGPU-Fertigung trotzdem ein Stück zurück ins eigene Lager.

Der N6-Prozess für den I/O-Tile wiederum ist schnell erklärt: TSMC hat in diesem Bereich seit Jahren Überkapazitäten, kämpfte zuletzt sogar mit der Auslastung. Den I/O-Tile deshalb, wie auch in den Jahren zuvor, günstig bei TSMC einzukaufen, ist für Intel also eine ganz naheliegende Wahl.

Welches Chips es am Ende auch sind, sie alle kommen auf einen Base-Tile und werden mit Intel Foveros-S „gepackt“ – in Anlehnung an CoWoS-S von TSMC. Die nun ganz eng miteinander verbunden gestapelten Chips sitzen in drei grundlegenden Konfigurationen am Ende auf einem klassischen BGA-Package und werden so dann im Notebook verlötet. Aber genau so war das auch schon bei Arrow Lake, Meteor Lake und sogar Lakefield, der als Testlauf für das Packaging-Verfahren galt. Der zugrunde liegende Basis-Tile ist mit der Fertigungsstufe P1227.2 (bisher war es Intel 22FFL (P1227.1)) zudem noch ziemlich der gleiche.

Der CPU-Tile im Detail: Mehr neue Kerne

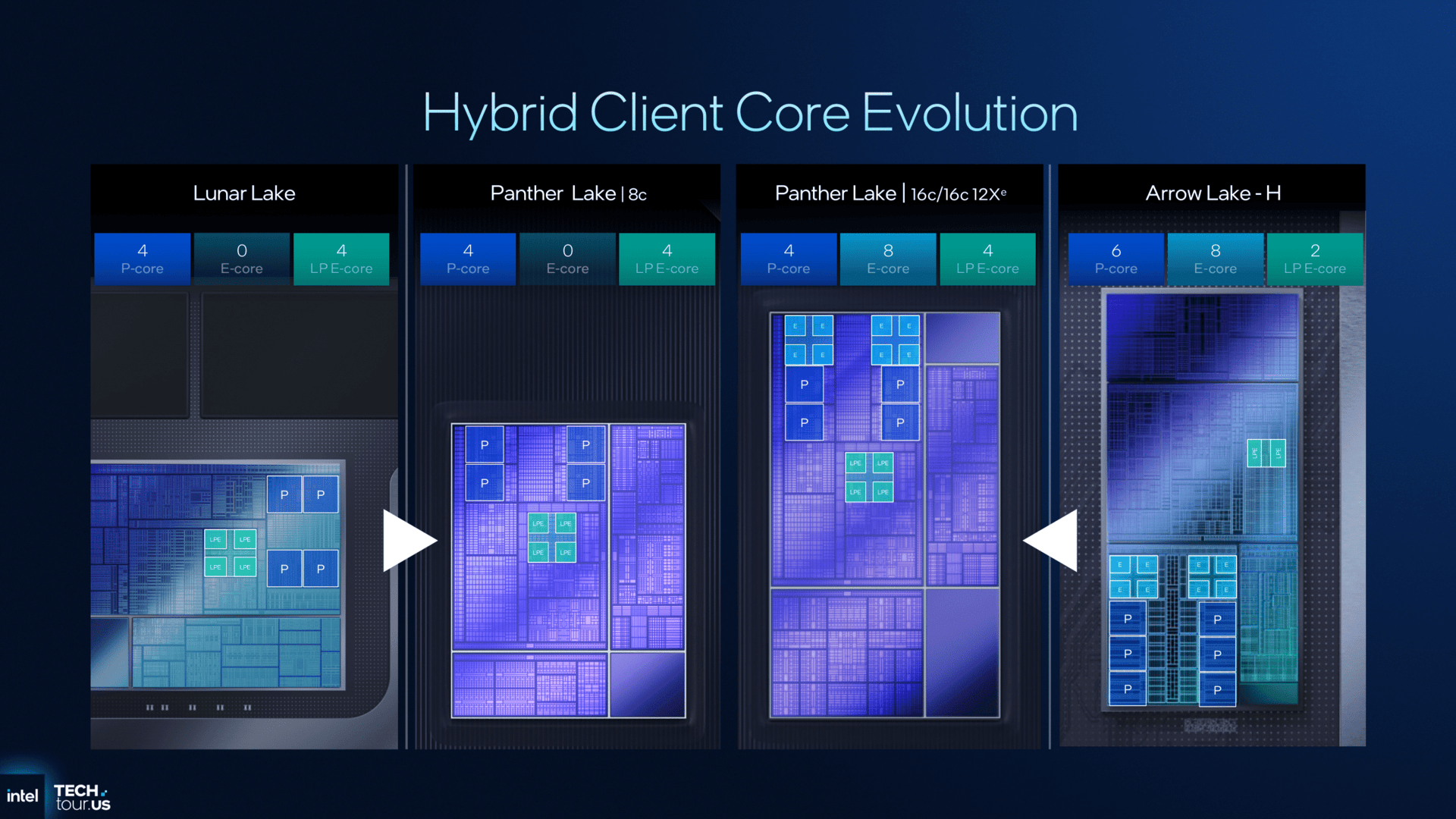

Panther Lakes CPU-Tile fußt auf den gesammelten Erfahrungen sowohl mit Lunar Lake als auch Arrow Lake.

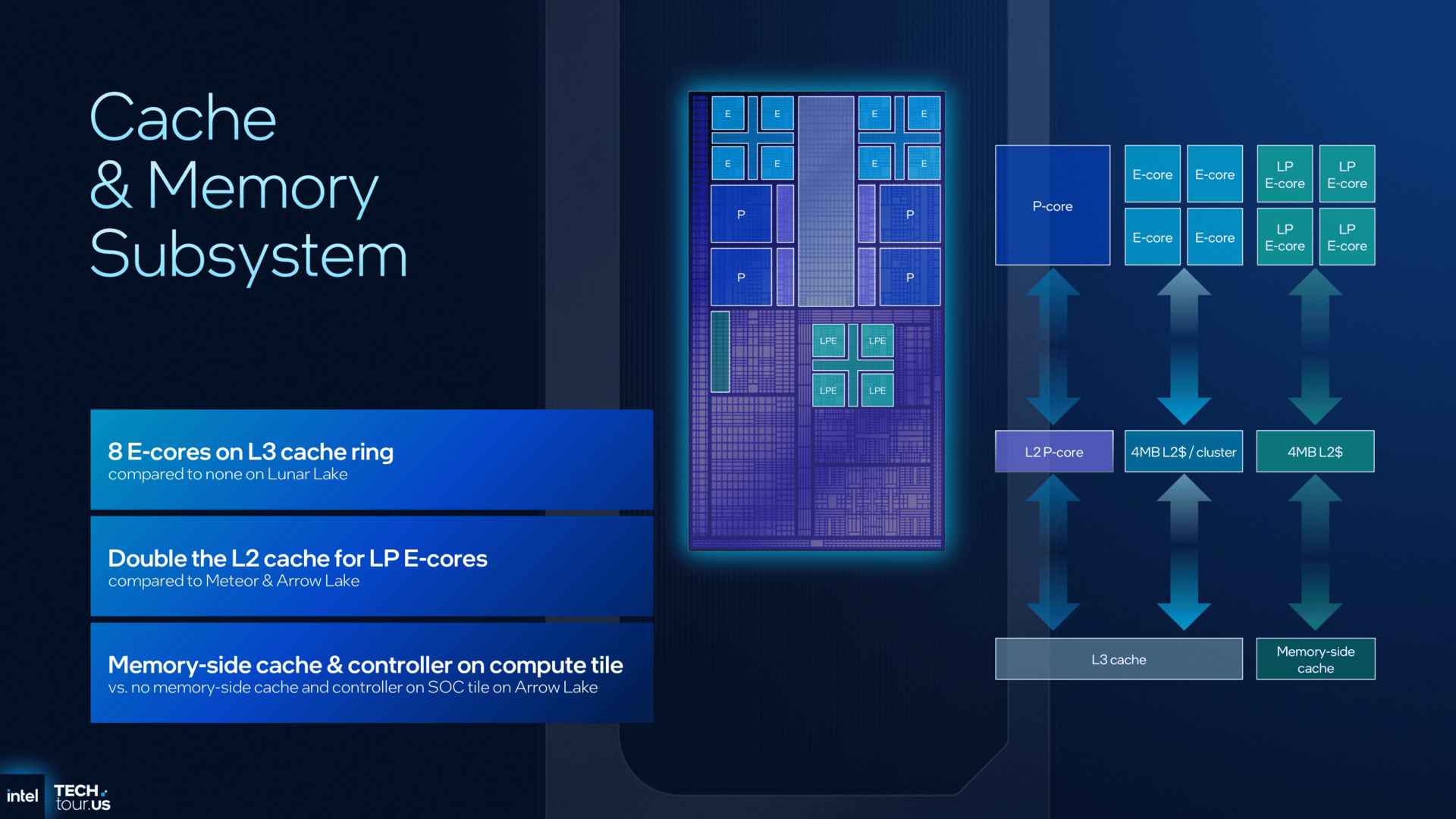

Arrow Lake setzte auf das klassische Intel-Design, Performance- und Efficiency-Kerne sitzen hier eng zusammengepackt an einem Ringbus in einem Chip – das macht Intel seit Arrow Lake alias 12. Generation Core so. Lunar Lake wiederum entkoppelte die P- und E-Cores: Die (LP)E-Cores wurden so viel stärker, aber auch unabhängig ansteuer- und regelbar, was vor allem auch dem Stromverbrauch zugute kam. Denn so muss nicht stets der ganze CPU-Cluster hochgefahren werden.

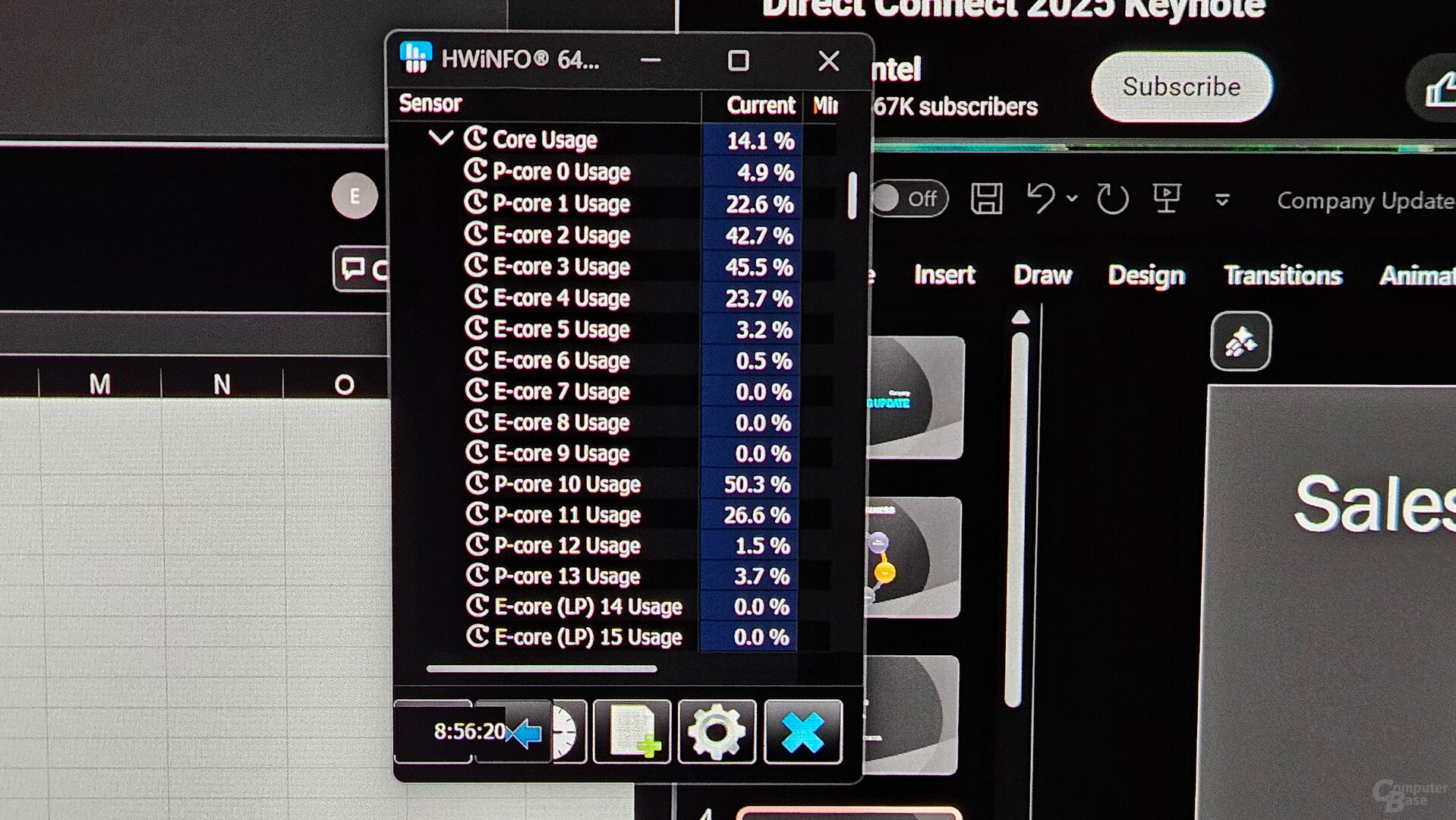

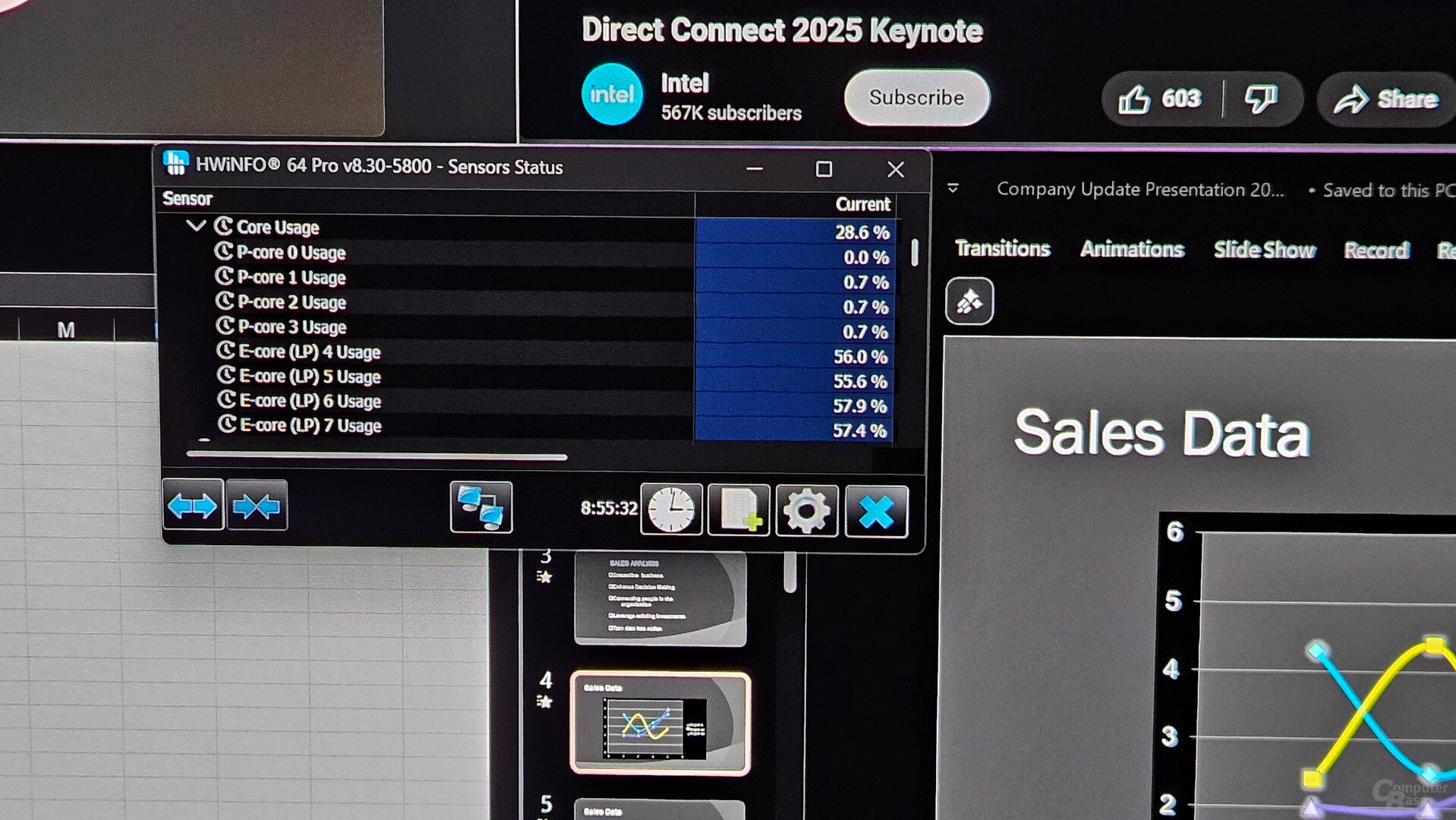

Panther Lake kombiniert nun beides: Es gibt sowohl die klassischen P- und E-Cores an einem Ringbus, aber auch noch ein zusätzliches LPE-Cluster. Ebenfalls neu: Es sitzt im gleichen Die und nicht wie bei Meteor Lake und Arrow Lake im ausgelagerten SoC-Tile. Auch bietet Panther Lake vier LPE-Kerne statt zwei mit viel mehr Leistung, um viele alltägliche Aufgaben auch wirklich übernehmen zu können, ohne dass das P- und E-Core-Cluster hochgefahren werden muss. Doch der Reihe nach.

Cougar Cove: die neuen Performance-Kerne

Die neuen Performance-Kerne tragen den Codenamen Cougar Cove. Diese setzen auf Lion Cove auf, wie sie in Lunar Lake und Arrow Lake als P-Core zum Einsatz kamen, vielfältige Optimierungen sollen nun primär Engpässe auflösen. Zudem wurde bekanntlich alles auf Intel 18A mit neuen GAA-Transistoren und Backside Power Delivery transferiert, es stand also die Thematik PPA (Power, Performance und Area) im Fokus – typisch für einen Notebook-Chip.

Im Detail lesen sich die Angaben zum neuen Kern Cougar Cove aber trotzdem nur wie ein kleiner Refresh zu Lion Cove. Dass dabei kleine Flaschenhälse aufgelöst werden, ist die Regel, auch größere Register und Speicher sind alles andere als ungewöhnlich. Die echten großen Neuerungen bleiben jedoch aus. Hyper-Threading respektive ein neues SMT gibt es in dieser Generation nicht, die vier großen Kerne bieten also vier Threads.

Wohl auch deshalb gibt Intel keine IPC-Zugewinne bei den P-Cores preis. Dass das optimierte Paket am Ende aber dennoch an Leistung zulegen kann, darauf deuten die ersten Leistungsprognosen im Single-Core-Test hin. Es könnte aber auch allein am Takt liegen.

Das SPEC-Ergebnis basiert traditionell auf der Leistung der P-Cores und hier liefert Panther Lake laut Hochrechnung über zehn Prozent mehr als Lunar Lake und Arrow Lake, wenn sie auf das gleiche TDP-Niveau eingeschränkt sind.

In diesem Setup hilft vermutlich aber eben die neue 18A-Fertigung, die bei gleicher TDP höhere Taktraten möglich machen sollte. Die Alternative: 40 Prozent geringerer Verbrauch für die gleiche Leistung. Für ein Notebook und die Akkulaufzeit ist diese Größe wiederum nicht unwichtig.

Darkmont: die neuen Efficiency-Kerne

Die aktualisierten E-Cores sind einmal mehr der Star – das war in den letzten Jahren schon des Öfteren der Fall. Aus der kleinen grauen Maus sind potente Kerne geworden, was vor allem für den mobilen Bereich nun langsam die Frage aufwirft, warum es denn überhaupt noch P-Cores braucht!?

Darkmont bringt gegenüber dem Vorgängern einmal mehr deutlich mehr Änderungen aufs Parkett als die P-Cores. Das ganze E-Core-Design wird noch breiter, kann mehr Aufgaben parallel abarbeiten. Beispielsweise ist das Out-of-Order-Window nun 416 Einträge groß. Bei Golden Cove gab es 512 Einträge – aber das ist ein P-Core!

Um den Datenaustausch zu beschleunigen, hilft ein schneller 4 MByte großer L2-Cache, den sich nach wie vor vier Kerne, die in einem Cluster gruppiert sind, teilen. Die insgesamt acht E-Cores haben am Ringbus aber auch Zugriff auf den bis zu 18 MByte großen L3-Cache.

Doch das gilt alles nur für den großen CPU-Tile: Im kleinen CPU-Die sind die E-Cores nicht vorhanden.

Im Layout wird auch klar, warum Intel die E-Cores deshalb am Rand platziert hat. Schnell konnte so das Design angepasst werden, um einen CPU-Die bereitzustellen, der diese E-Cores „einfach abschneidet“.

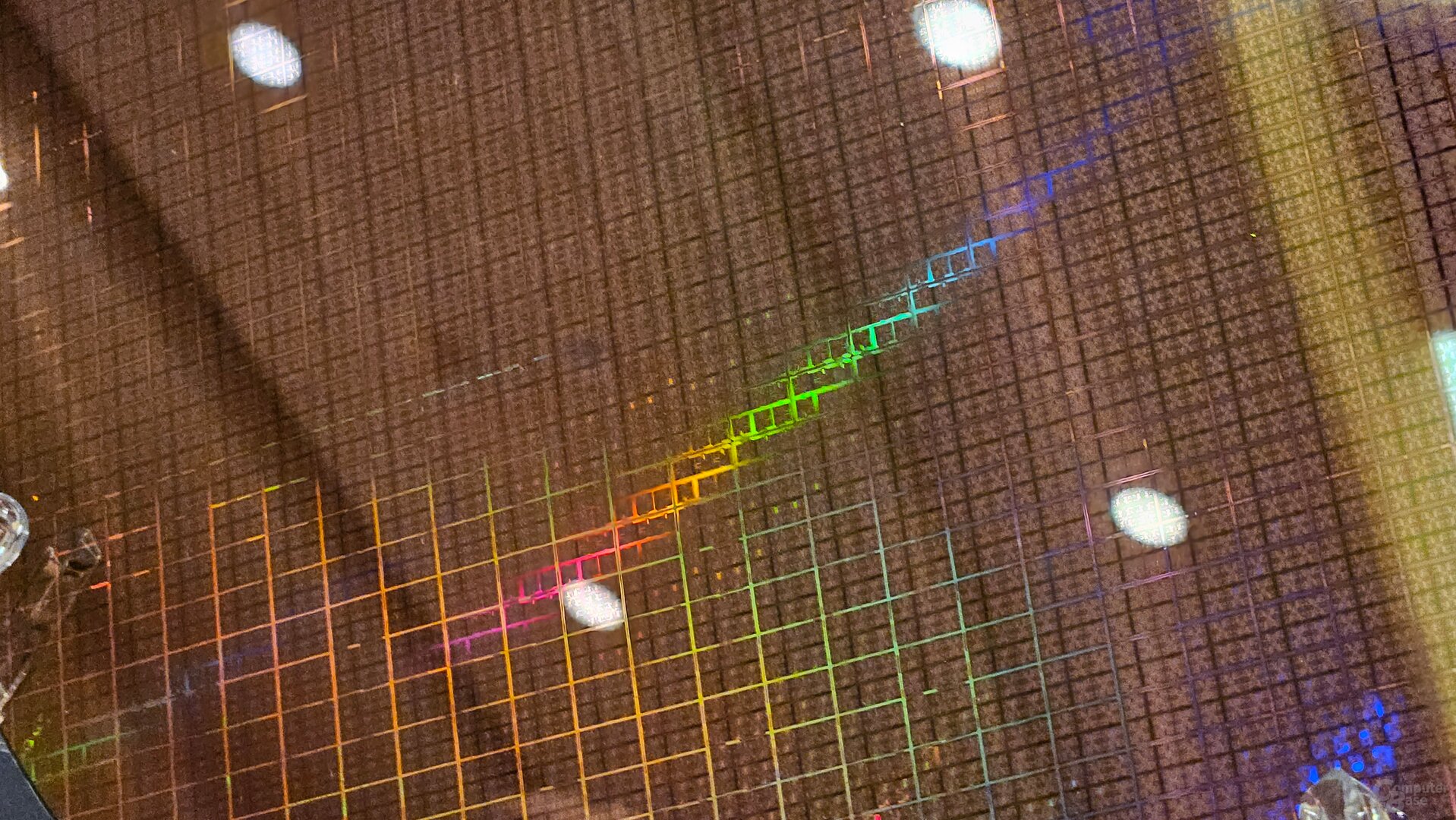

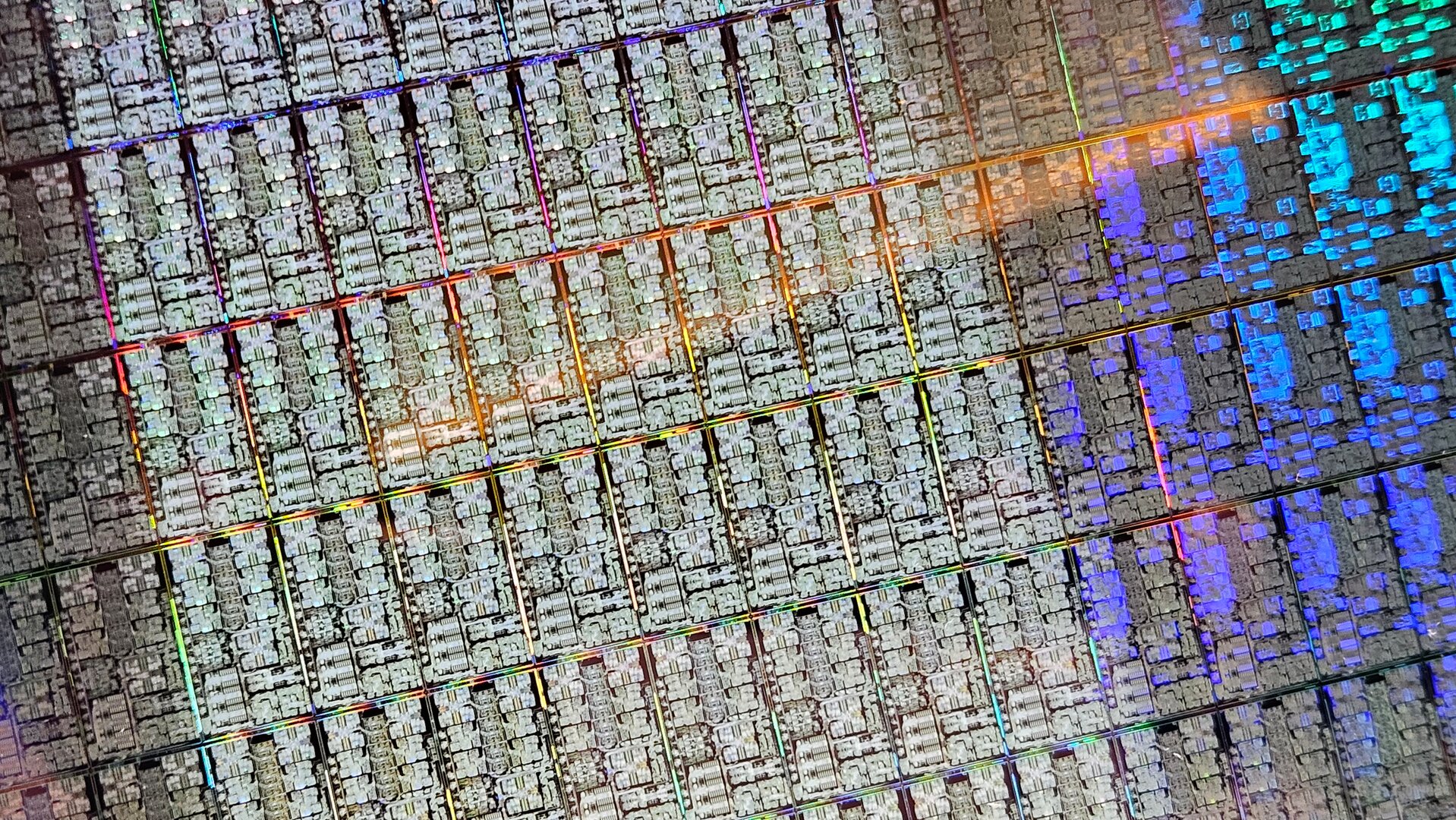

Der Blick auf den Wafer mit CPU-Tiles von Panther Lake in der großen Konfiguration zeigt dies ebenfalls schön: Die größeren Cluster am Ende sind die E-Cores, daran angeknüpft vier P-Cores. Trotz Verkleinerung nimmt auch die NPU für den CPU-Tile weiterhin ziemlich viel Platz ein.

In der Panther-Lake-Präsentation wollte Intel zum IPC-Gewinn der Darkmont-Kerne ebenfalls nichts sagen. Am darauffolgenden Tag gab es jedoch die Details zu Intel Clearwater Forest (Xeon), der auch auf Darkmont-Kerne setzt. Hier erklärte Intel einen IPC-Zuwachs von 17 Prozent gegenüber Crestmont im Server. Ein Vergleich zu den mobilen Lösungen ist aber kompliziert, denn da gab es bereits eine neue Zwischenstufe, Skymont. Dort wiederum hatte Intel aber nur wenig aussagekräftige Vergleiche mit LPE-Cores angestellt.

ComputerBase hat daraufhin nachgefragt, ob die Kerne identisch ausfallen und sich so letztlich der IPC-Zuwachs auch auf Panther Lake umlegen lässt. Intel erklärte dazu zwar, dass es leichte Unterschiede gibt, aber die Xeon-Aussagen auch für Intel Core Ultra gelten sollten.

Im Ergebnis sind die neuen E-Cores in etwa so schnell wie Raptor Cove – das war der P-Kern in der 13. und 14. Core-Generation. Und dafür müssen in Panther Lake keine 6 GHz angelegt oder 60+ Watt verbraucht werden. Vor allem im Einsatz bei geringem Verbrauch sind die Neulinge erneut viel besser. Die P-Cores sind wie bei aktuellen Arm-Design nun nur noch „Premium-Kerne“ für extreme Spitzenlasten, alles andere wird von den darunter liegenden erledigt.

Das Bild von Darkmont, welches Intel liefert, ähnelt dabei letztlich aber dennoch sehr stark Skymont, wie er als LPE-Kern bereits in Lunar Lake zugegen war. Auch diese konnten im Low-Power-Bereich bereits Raptor Cove übertreffen. Darkmont kann das nun vielleicht noch etwas besser, ein sehr großer Unterschied zu Skymont dürfte dabei aber dennoch nicht herauskommen. Wohl auch deshalb nennt Intel auch für Panther Lakes E-Cores keinen IPC-Zuwachs, denn er dürfte sehr gering ausfallen.

Dazu passen dann auch die Prognosen der Mehr-Kern-Performance von Panther Lake gegenüber den beiden Vorgängern, die wiederum auch zeigen: Die Leistung ist dennoch sehr hoch. Lunar Lake wird wie erwartet überdeutlich abgehängt, mit nur 4P+4E-Kernen hat diese Lösung keine Chance. Aber selbst gegenüber Arrow Lake-H, die immerhin mit 6P+8E+2LPE unterwegs sind, liegt Panther Lake mit 4P+8E+4LPE in Front. Vier starke LPE-Cores wiegen zwei P-Cores plus zwei nutzlose LPE-Cores in Arrow Lake-H in dem TDP-Bereich mehr als auf. Alternativ liefert Panther Lake die gleiche Multi-Core-Leistung wie Arrow Lake-H bei 30 Prozent weniger Stromverbrauch.

Die neuen LPE-Cores: Noch einmal Darkmont!

LPE-Cores, also Low Power Efficiency Cores, haben erst einmal richtig funktioniert: Bei Lunar Lake, wo sie im CPU-Tile lagen. Bei Meteor Lake und auch bei Arrow Lake waren die zwei in den SoC-Tile ausgelagerte E-Kerne, die extrem niedrig getaktet waren, hingegen quasi nutzlos – der Tile mit den P- und E-Cores lief trotzdem immer.

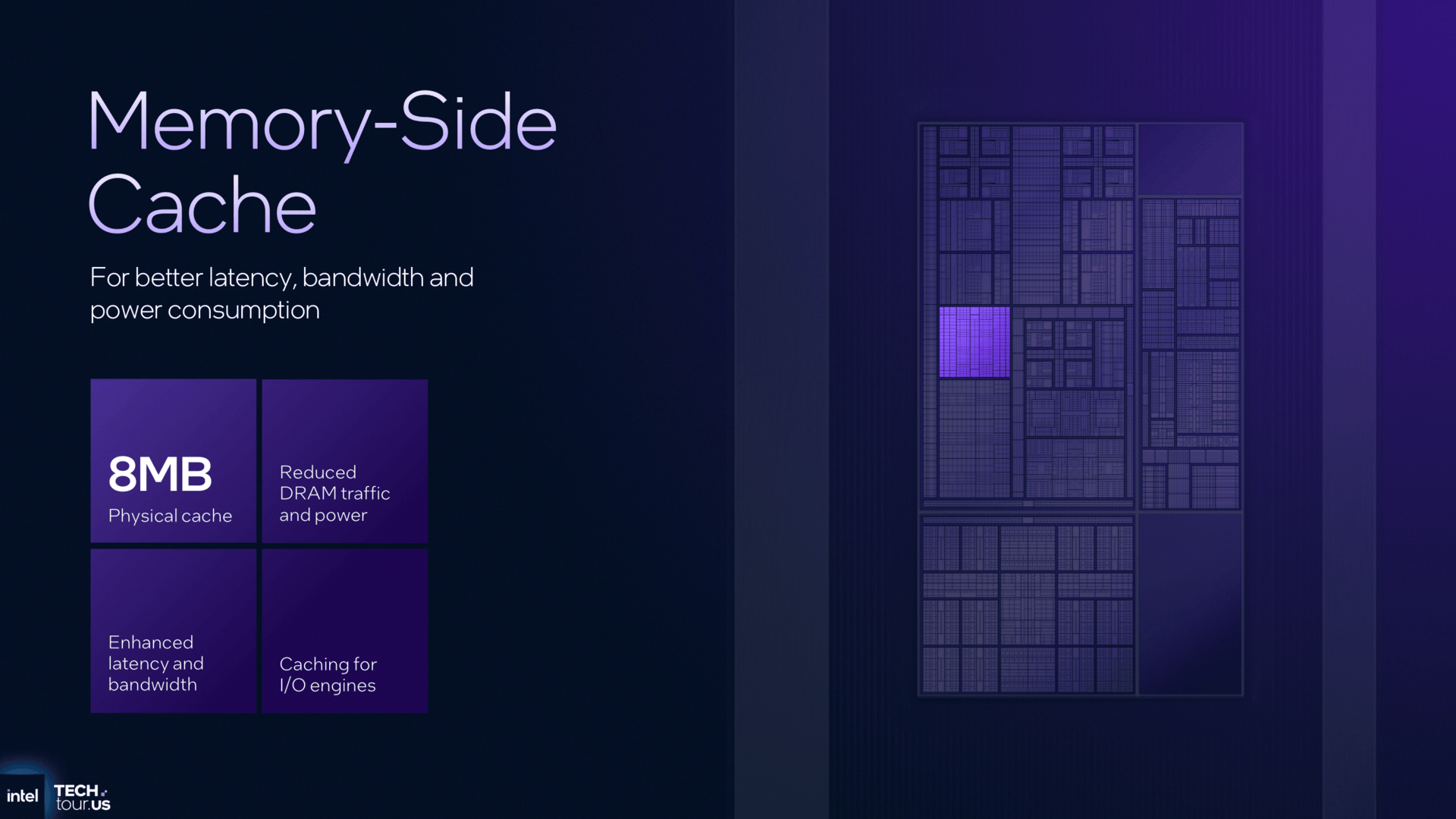

In Panther Lake gibt es nun wie in Lunar Lake einen unabhängigen LPE-Cluster mit vier Kernen, der auf dem gleichen CPU-Die liegt wie all die anderen Prozessorkerne. Der Cluster nutzt die gleiche Darkmont-Architektur und kann auch auf den 8 MByte großen Side-Cache zugreifen, der neben dem Shared-L2-Cache in unmittelbare Nähe liegt.

Das Ziel dieses unabhängigen LPE-Clusters ist klar: Alltägliche (leichte) Aufgaben soll allein er übernehmen, während der große CPU-Cluster weiter schlafen liegt. In erste Vorführungen vor Ort, in denen drei gleiche Systeme mit Lunar Lake, Arrow Lake-H und Panther Lake im Einsatz waren, konnte der Neuling im Durchschnitt einen noch geringeren Verbrauch für die gleiche Arbeit vorweisen. Vor allem gegenüber Arrow Lake-H war dies überdeutlich, dessen LPE-Cores nutzlos sind und so der große „stromfressende“ CPU-Tile stets hochgefahren werden muss.

Unterm Strich ist Panther Lake im CPU-Bereich das klassische mobile Design, welches eine neue Fertigung einführt. Früher hieß das bei Intel „Tick“, also die Einführung eines neues Prozesses, während bei „Tock“ in Intels Tick-Tock-Modell eine echte neue Architektur im gleichen Prozess übernahm – das wird Nova Lake im zweiten Halbjahr 2026 übernehmen. Das Endergebnis lässt dennoch hoffen: Der noch geringerer Verbrauch als bei Lunar Lake mit höherer Leistung und der Entscheidung den „SoC-Tile“ wieder in den CPU-Tile zu verlegen klingen vielversprechend. Das Gesamtpaket Panther Lake könnte demnach ziemlich rund werden.

Speichercontroller: LPDDR5X-9600-Support

Panther Lake kann nun LPDDR5X-9600 ansprechen, das ist ein großes Update gegenüber Lunar Lake. Auch klassischer DDR5-Speicher ist weiter mit dabei, mit bis zu 7.200 MT/s wird hier ebenfalls ein Wert offiziell unterstützt, der bisher seinesgleichen sucht. Auf Rückfrage von ComputerBase, ob das CU-DIMM bedeutet, lautete Intels Antwort: Nein, klassische U-DIMM reicht aus.

Je nach Modell schränkt Intel den Speichersupport aber ein. Die kleinste Lösung wird maximal 6.800 MT/s bekommen, das mittlere Design 8.533 MT/s und erst der Vollausbau gepaart mit der großen Grafik bekommt den schnellsten Speicher nach Standard LPDDR5X-9600 – genau die GPU braucht den aber auch.

Bevor die CPU auf den Arbeitsspeicher zurückgreifen muss, greifen allerdings die ganze Cache-Stufen. Die P-Cores setzen auf 256 KByte L1-Cache und 3 MByte L2-Cache pro Kern, Darkmont als E- und LPE-Core nutzt 96 KByte L1-Cache und teilt sich mit drei weiteren Kernen 4 MByte L2-Cache. Die P- und E-Kerne teilen sich am Ende noch einen bis zu 18 MByte großen L3-Cache.

Ebenfalls mit dabei und zuvor bereits bei den LPE-Kernen kurz angerissen, ist der Side Cache. Als weitere Zwischenstufe vor dem DRAM soll er Zugriffe direkt abfangen und bearbeiten. Das wiederum geschieht sehr flott und erhöht letztlich die IPC des Prozessors.

Eine NPU mit 50 TOPS

Die neue NPU hat zwar weiterhin nur 50 TOPS, sie ist laut Intel aber ein großer Schritt nach vorn beim Thema Effizienz. Nicht nur ist sie deutlich kleiner geworden, sie sei auch viel stromsparender. Damit werden die größten Kritikpunkte der bisherigen NPUs von Intel adressiert.

Es gibt aber auch leistungsrelevante Anpassungen an der NPU, die die 50 TOPS nicht widerspiegeln. Die Unterstützung für INT8 und FP8 neben FP16 ist vor allem im mobilen Bereich ein Schritt nach vorn, denn Arbeiten im FP8-Format sind deutlich weniger speicherhungrig und energiesparender.

Unterm Strich macht Intel durch die Blume aber erst einmal klar: Mehr als 50 TOPS braucht es aktuell nicht, zumal diese durch passende Software auch erst einmal wirklich abgerufen werden müssen. Die Windows-Copilot+-Zertifizierung ist damit gesichert, alle Aufgaben, die die NPU überschreiten, werden ohnehin von der viel schnelleren GPU erledigt – also so, wie bisher auch schon. Denn diese bietet in der großen Version immerhin 120 TOPS. Im Marketing bietet Panther Lake am Ende also insgesamt „bis zu 180 TOPS“. Diese sind aber wie gehabt nie gleichzeitig nutzbar, die Angabe deshalb letztlich eigentlich sinnlos.

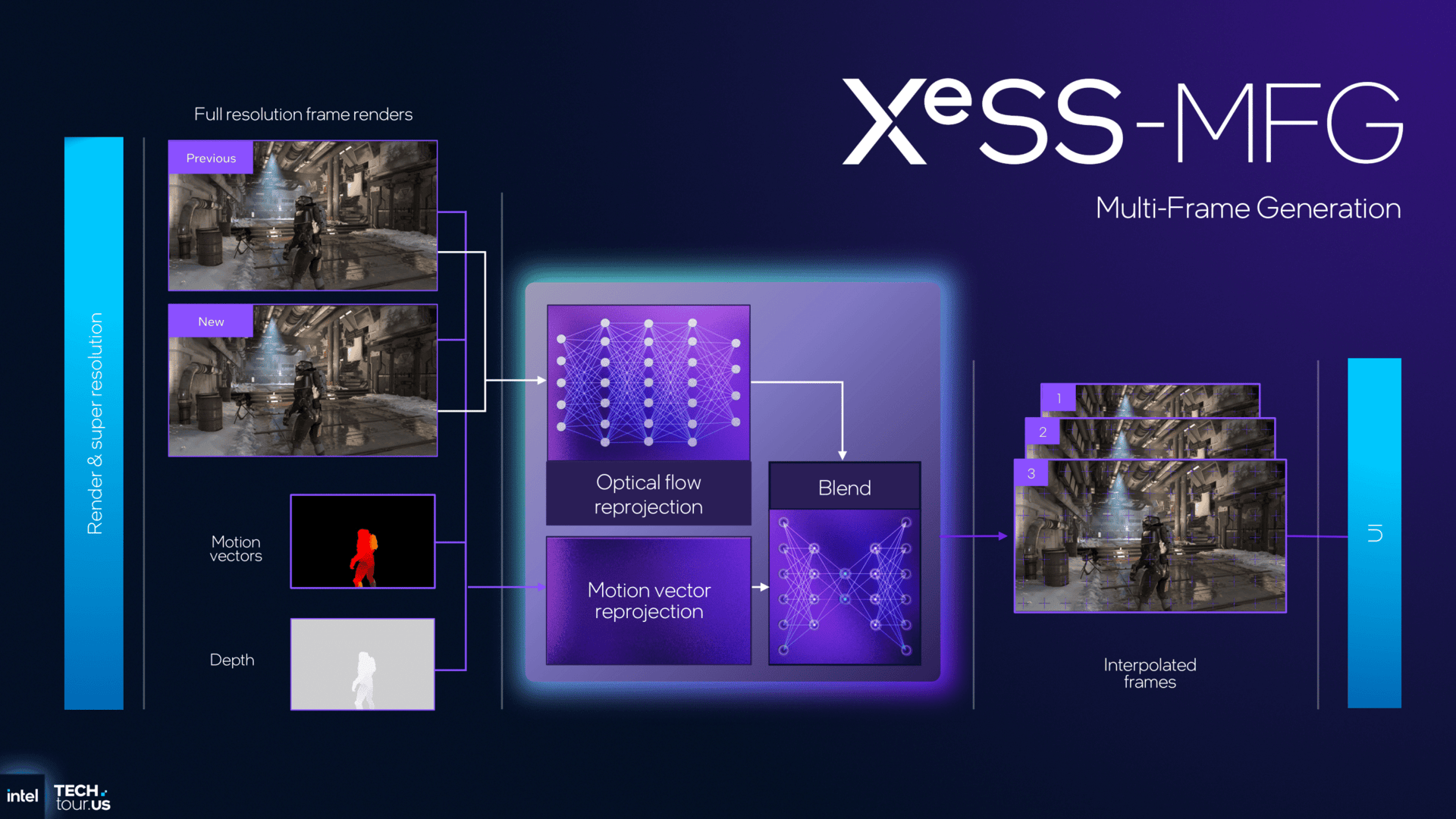

Der GPU-Tile im Detail: Xe3 mit MFG

Die neue Grafikeinheit setzt erstmals auf Xe3, wird aber weiterhin als B-Serie laufen – so wie Xe2 alias Battlemage in der Arc-B-Serie. Vor Ort sorgte dies für Schulterzucken. Intel versuchte zu beschwichtigen und erklärte, dass Xe3 im Notebook eben eher eine Evolution von Lunar Lake sei, B-Series so letztlich besser passt. Die echte C-Series dürfte dann mit diskreten Karten folgen, immerhin hat Intel eine Roadmap mit Xe3P gezeigt. „Celestial“ scheint also weiterhin eingeplant zu sein.

Die Xe3-Kerne im Detail

Doch zurück zur Xe3-GPU, in die laut Intel viel Arbeit geflossen sein soll. Wie bereits erwähnt wird diese in zwei Ausbaustufen bei Panther Lake zum Einsatz kommen: Einmal mit vier Xe-Cores (Intel 3) und in der großen Lösung mit 12 Xe-Cores (TSMC N3E). Letztere soll für performante Notebooks genutzt werden, ohne dass eine diskrete Grafik verbaut wird, bei der kleinen GPU bleibt die diskrete zusätzliche Grafikkarte optional. Hierfür stellt der darauf abgestimmte I/O-Die acht PCIe-Lanes der fünften Generation zur Verfügung.

Dass die Xe3-Grafik gegenüber Lunar Lake im Durchschnitt 50 Prozent zulegt, verdankt sie in erster Linie wohl den 50 Prozent zusätzlichen Kernen, die zudem mehr elektrische Leistung aufnehmen können und dabei auch eine größere Fläche belegen. Die Kerne an sich wurden auch überarbeitet. 33 Prozent größere L1-Caches und gar 50 Prozent größere L2-Caches sollen dabei helfen, dass die Daten nicht den Umweg über den langsamen RAM gehen müssen.

Mit mehr Kerne und größeren Caches, einer insgesamt größeren Fläche und mehr Leistungsaufnahme letztlich eine höhere Leistung als Lunar Lake zu bieten, ist jedoch alles andere als überragend. Vielmehr ist es sogar etwas enttäuschend. Aber auch hier bleibt abzuwarten, was die Praxis bringt.

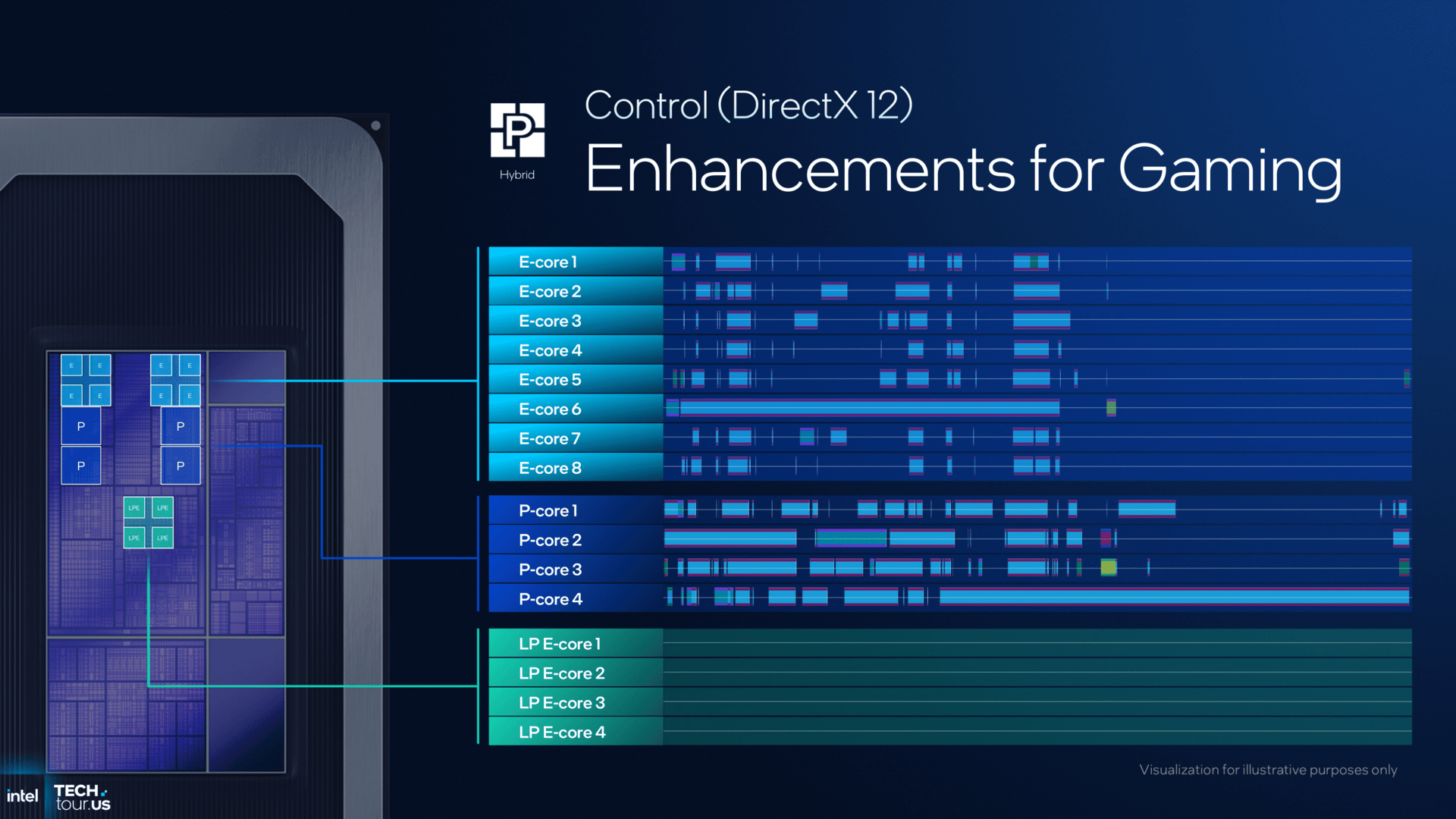

Mehr Energie für die Grafikeinheit heißt aber auch, dass diese irgendwo abgezweigt werden muss. Die Lösung: Statt der P-Cores können in Spielen auch die E-Cores priorisiert werden. Angesichts einer Performance, die bei geringerem Verbrauch oberhalb der P-Cores in Core i-14000 liegt, und der Tatsache, dass mobile GPUs nicht so schnell wie Desktop-Modelle sind, könnte das aber durchaus ohne Leistungsverlust auf CPU-Seite vonstatten gehen.

XeSS MFG (alias XeSS 3) kommt

Wegen der weiterhin eher geringen Leistung wird Intel deshalb noch mehr auf XeSS setzten. Auch bei Intel kommt nun Multi Frame Generation zum Einsatz, um selbst auf kleinen integrierten GPUs ein noch (sichtbar!) flüssigeres Spielerlebnis zu bieten. Vor Ort lief das neue Painkiller mit 200 FPS – MFG sei Dank. Abwärtskompatibel soll XeSS 3 auch zu Battlemage sein, der Start aber wohl erst mit Panther Lake erfolgen.

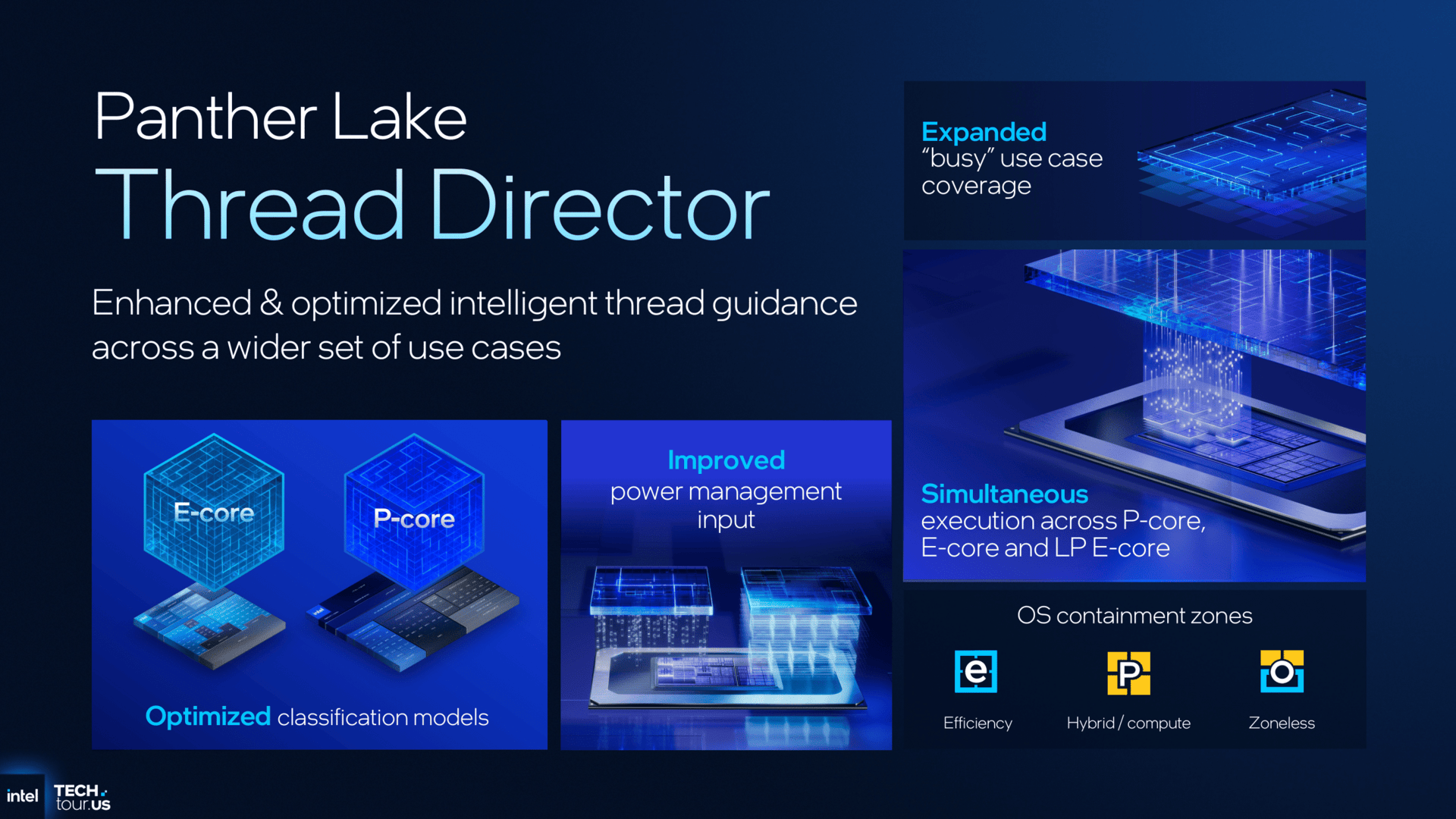

Thread Director favorisiert LPE-Cores

Der Thread Director, wie Intel das Scheduling seit Alder Lake nennt, da es sich um die Zuweisung der jeweiligen Aufgaben auf die passenden Kerne kümmert, erfährt in Panther Lake ein weiteres Update. Dass im Notebook die kleinen Kernen noch mehr in den Fokus rücken, ist keine Überraschung. Dennoch können, je nach Anwendung, die LPE-Cores auch mal Schlafen liegen.

Intelligente Energieprofile im Betriebssystem

Auch die bisherige Energieoptionen beispielsweise unter Windows hat sich Intel angesehen und Optimierungen auf den Weg gebracht. Denn die letzten Lösungen, in denen erst ein OEM gewisse Profile festlegt hat und Windows zusätzlich seine eigenen bietet, diese sich mitunter ergänzen, oder aber auch mal ausschließen, brachte selten das Optimum hervor: Denn plötzlich gab es neben drei Windows-Profilen auch noch fünf Herstellerprofile.

Mit Intel Intelligent Experience Optimizer will Intel eine neue Alltagslösung am Markt etablieren. Dieser erkennt selbstständig ob das System nicht gefordert ist und wechselt entsprechend in einen Leistungszustand mit geringerem Energiebedarf. Auf der anderen Seite erhöht es das Powerprofil, wenn Leistung benötigt wird. In internen Tests wurden so schnell zweistelligen Leistungszuwächse erzielt, wobei zu beachten ist, dass es hier schlichtweg schon auf den Ursprungszustand des Notebooks ankommt.

Für Endkunden dürfte dies durchaus nützlich sein, Testredaktion wiederum vor einige Herausforderungen stellen. Denn ob das System dann jedes Mal das gleiche macht, bleibt abzuwarten.

IPU und Media Engine auf neuestem Stand

Direkt neben den LPE-Cores sind die aktualisierte IPU und Media Engine zu finden. Die Position ist auch hier nicht zufällig gewählt, denn sie erlaubt kurze Wege zur iGPU, aber im günstigsten Fall braucht es eben nur die LPE-Cores zur Unterstützung, um dann auch Bilder auszugeben oder beispielsweise die verbaute Kamera zu nutzen, während der ganze große CPU-Cluster weiter schläft.

I/O-Tile mit nur kleinen Anpassungen

Beim I/O-Tile gibt es bei Panther Lake wenig Neues zu berichten. Im mobilen Umfeld braucht es auch keine unzähligen Anschlüsse und die kabellose Konnektivität ist Trumpf. Neu unterstützt wird beispielsweise Bluetooth Auracast. WiFi 7 wird nach wie vor über CNVi realisiert, intern gibt es weiterhin nur Thunderbolt 4 – für vor allem stromsparende Notebooks ist dies jedoch ausreichend. Thunderbolt 5 wird unterstützt, dann aber wie aktuell bereits üblich über diskrete Controller-Chips. Und warum gibt es den einen I/O-Tile-Chip in zwei Konfigurationen?

In der kleinen Version bietet er aus Stromspargründen nicht genug PCIe-Lanes um eine diskrete GPU anzusprechen. Dies ist nur im Vollausbau des I/O-Tiles, die vermutliche Core Ultra 300H nutzen wird, möglich. Dass der I/O-Tile letztlich unter der Haube der gleiche ist, hat eher mit der Fertigung zu tun. Wegen ein paar mm² Einsparung eine neue Maske aufzulegen, wenn auf der anderen Seite weiterhin zwei Filler-Tiles für ein stabiles Package sorgen müssen, rechnet sich nicht. So wird der kleine I/O-Tile letztlich nur kastriert, das Silizium ist identisch.

Einschätzung und Ausblick

Intel Panther Lake tritt – voraussichtlich als Core Ultra 300 – ab Anfang 2026 das Erbe von gleich zwei aktuellen Lösungen im Notebook an: Lunar Lake (Core Ultra 200V) als DRAM-on-Package-Überraschung des letzten Jahres und Arrow Lake (Core Ultra 200H), dem klassischen Intel-Design aus diesem Jahr. Panther Lake vereint Vorzüge beider Lösungen, auf dem Papier und in den ersten Demos sieht das Ergebnis sehr vielversprechend aus.

Dabei sind es bei Panther Lake die Summe der Teile und einige entscheidende Chiplet-Design-Anpassungen, die den Unterschied machen sollten, während einige Aspekte wiederum nur kleine Fortschritte zu machen.

Die Performance-Kerne sind bestenfalls ein kleiner Refresh mit minimalem Leistungszuwachs, die E-Cores wiederum ragen gepaart mit den neuen LPE-Cores deutlich heraus. Denn sie bieten bei weniger Leistungsaufnahme die Leistung gar nicht mal so alter P-Cores. Bis zu 12 Stück an der Zahl sorgen für hohe Multi-Threading-Leistung. Auch die LPE-Cores wie bei Lunar Lake nicht auszulagern und damit ein großes Problem von Arrow Lake-H zu beheben, dürfte einen großen Effekt haben. Das Gleiche gilt für den zurück in den CPU-Tile geholten Speichercontroller.

Die NPU wiederum ist eher ein Effizienz-Update, die Xe3-Grafik nur im großen Modell ein Schritt nach vorn, in diesem Fall aber auch erkauft durch größere Fläche und mehr Energiebedarf – so konnte man auch in der Vergangenheit schneller werden.

Nichtsdestoweniger sieht Panther Lake mit Intel 18A aktuell nach einem Schritt in die richtige Richtung aus. In der Praxis müssen sich diese Vorschusslorbeeren am Ende aber auch verdient werden.

Panther Lake im Podcast

Als Ergänzung zum Bericht hat sich Volker diese Woche gemeinsam mit Jan im Podcast über Panther Lake unterhalten. Ab Minute 39:10 gibt es darüber hinaus den Bericht vom Besuch der Fab 52 in Arizona zu hören.

ComputerBase hat Informationen zu diesem Artikel von Intel im Vorfeld und im Rahmen einer Veranstaltung des Herstellers in Chandler, Arizona, unter NDA erhalten. Die Kosten für Anreise, Abreise und vier Hotelübernachtungen wurden von dem Unternehmen getragen. Eine Einflussnahme des Herstellers auf die oder eine Verpflichtung zur Berichterstattung bestand nicht. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.

Apps & Mobile Entwicklung

Intel Clearwater Forest mit 288 Kernen im Detail

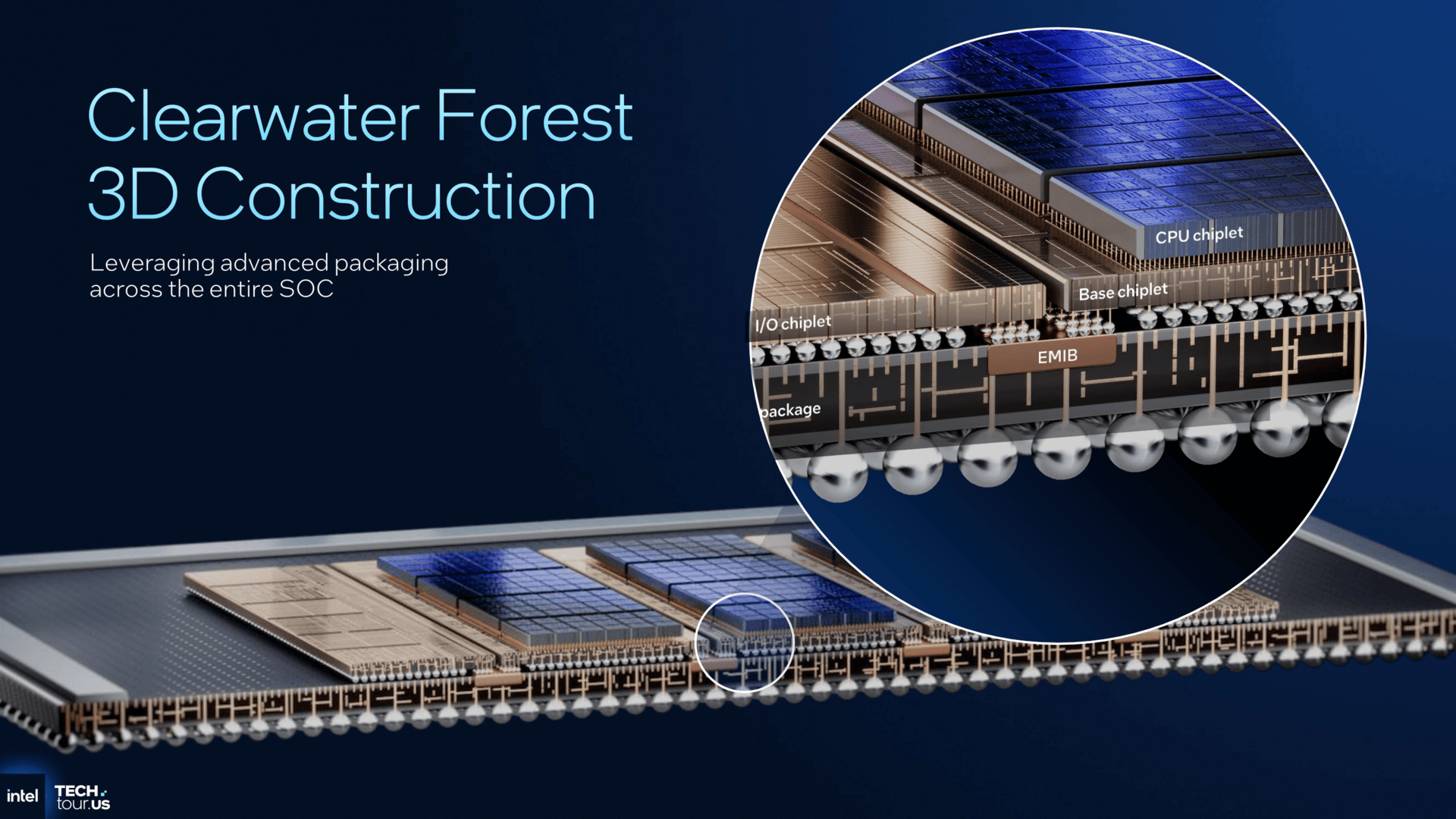

Bei Clearwater Forest nutzt Intel erstmals das neue Die-Stacking im X3D-CPU-Stil. Die neuen Xeon 6+ sind damit ein Schritt in die Zukunft, denn die Technologie wird bald in weitere Bereiche vordringen – einschließlich PC-Chips. Für Server sind damit zum Auftakt bis zu 288 schnellere Kerne möglich.

Viele Kerne mit einem Server-Prozessor bereitzustellen, funktionierte in den letzten Jahren nur noch über Tiles bzw. Chiplets: Viele relativ kleine, aber immer gleiche Chips wurden zusammen auf dem Package vereint, die Summe ihrer Chips ergab den Vollausbau des Prozessors. Bis zu 16 Chiplets kamen bis dato auf einem Package zum Einsatz – bei AMD. Und um dennoch sehr viel L3-Cache anzubieten, wurde er auf oder unter die Chiplets gelegt – bei AMD.

Auch Intel hatte mit Sierra Forest-AP zuletzt Xeon-CPUs mit bis zu 288 Kernen geboten. Doch sie lagen in zwei großen 144-Chips vor. Mit Clearwater-Forest geht Intel jetzt dem AMD-Weg. Wie bei Panther Lake (Details) setzen die CPU-Chiplets dabei auf Intel 18A.

Das ist Intel Clearwater Forest

- Einsatz in bestehender Plattform (Birch-Stream-AP)

- 288 E-Cores wie Sierra Forest-AP

- Aufgeteilt in 12 × 24 statt 2 × 144 Kerne

- Neue Darkmont-E-Cores

- Großer L3-Cache im Base-Tile unter den CPU-Chiplets

Die Plattform bleibt dieselbe

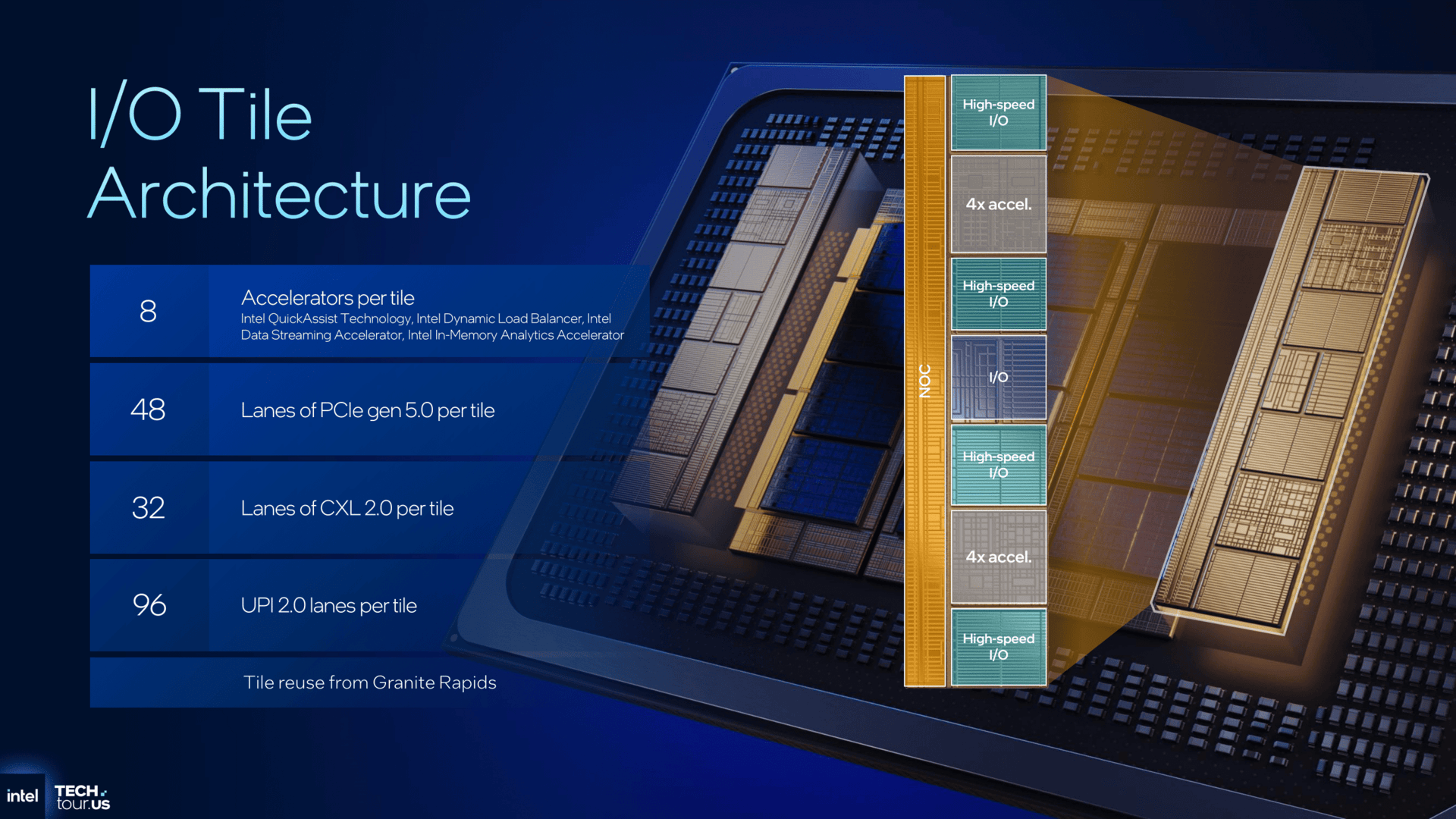

Intel Clearwater Forest kommt als Xeon 6+ auf den Markt. Warum Xeon 6+? Weil die neuen Prozessoren in den gleichen Sockel wie die CPUs der Serie Intel Granite Rapids-AP alias Xeon 6 passen, die aktuelle Birch-Stream-AP-Plattform wird also weiter genutzt. Weil bei beiden CPU-Familien der gleiche I/O-Tile genutzt wird, sind auch alle Anschlüsse, Ports und PCIe-Lanes identisch.

Sechs Mal mehr Chiplets

Clearwater Forest steht im Endeffekt für die zweite Generation eines Intel-Prozessors im Profi-Bereich, der nur auf Efficiency-Kerne (E-Cores) setzt. Die erste Generation gab es als Xeon 6900E als Sierra Forest-AP bereits mit bis zu 288 Kernen für ausgewählte Kunden, zwei CPU-Tiles mit je 144 aktiven Kernen waren die Basis.

Mit Clearwater Forest geht Intel jetzt den AMD-Instinct-MI300A-Weg: Statt zwei große Dies gibt es 12 kleinere CPU-Tiles mit jeweils 24 Kernen in sechs Clustern zu 4 Kernen mit geteiltem L2-Cache.

Bei einem vor Ort ausgestellten Wafer sind diese Dies mit je sechs Vier-Kern-Clustern auch gut erkennbar. Selbst dieser Sechserblock ist letztlich vergleichsweise klein, der Chiplet (oder Tile-Ansatz, wie Intel ihn nennt) geht auf. Denn größere Chips mit mehr Kernen in einer neuen Fertigung zu produzieren, geht schnell auf die Ausbeute. Kleine Chips hingegen können schneller in größerer Menge voll funktionsfähig bereitgestellt werden. Das hat AMD vor Jahren bei Epyc und Ryzen und auch Instinct erkannt.

Darkmont-Kerne wie bei Panther Lake

Neu sind aber auch die Kerne an sich. In Clearwater Forest wird Intel wie in Panther Lake neue Darkmont-E-Cores verbauen. Diese stellen gegenüber der Vorgängerlösung eine deutliche Verbesserung dar, denn Sierra Forest nutzt lediglich Crestmont-Kerne. Zur Einordnung: Für Lunar Lake und Arrow Lake im Consumer-Markt hatte Intel zwischendrin bereits Skymont aufgelegt, in der Roadmap heißt es also Crestmont -> Skymont -> Darkmont.

Mit den 17 Prozent IPC-Zuwachs von Darkmont in Clearwater Forest gegenüber Crestmont in Sierra Forest lässt sich deshalb auch erst einmal wenig anfangen, außer, dass eben die Leistung pro Takt gestiegen ist. Skymont als nicht genutzte Zwischenlösung wurde im mobilen Segment zwar mit Crestmont verglichen, dort aber in Form der extrem schwachen und kastrierten LPE-Cores, der Zuwachs lag so teils bei über 50 Prozent. Ein sauberer Vergleich war auch da nicht drin. Eventuell wird Intel dies zum echten Marktstart der Produkte mit Darkmont noch einmal nachholen.

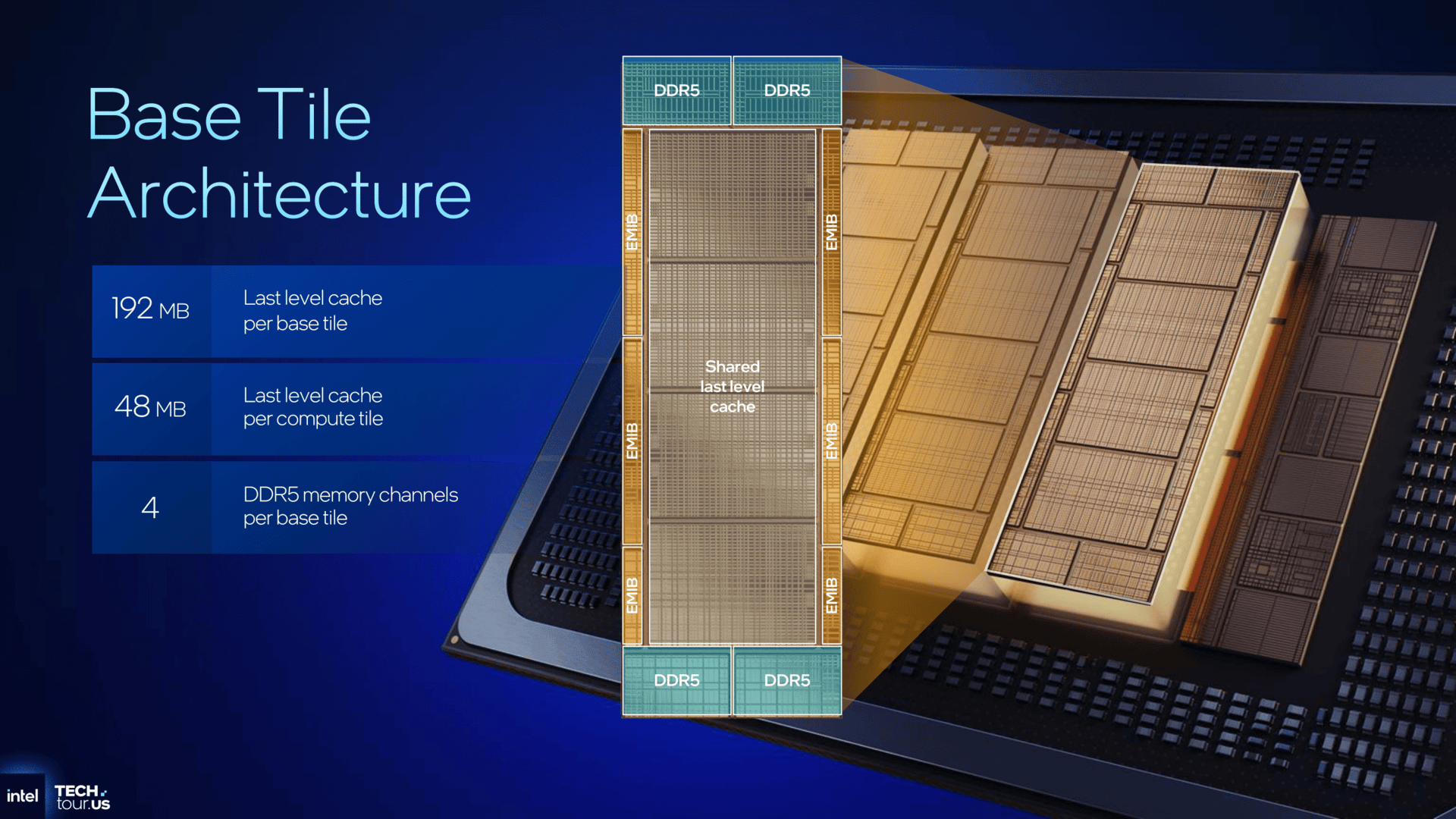

Drei Base-Tiles tragen je vier CPU-Tiles

Jeweils vier der 24-Kern-Chips sitzen auf einem Intel-3-Base-Tile, davon wiederum gibt es insgesamt drei. Summa summarum werden so die 288 Kerne bereitgestellt.

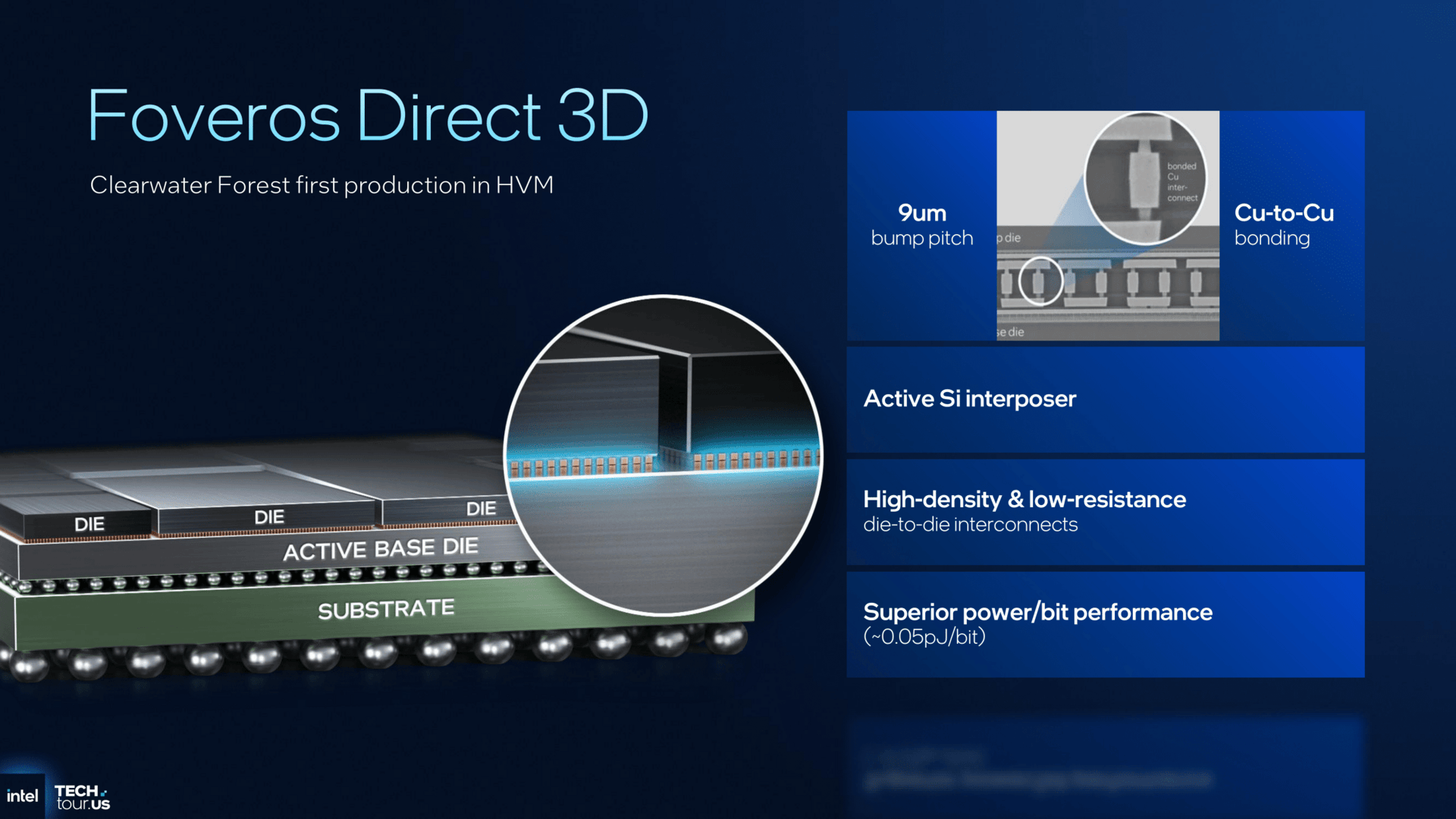

Der Base Tile ist aber nicht mehr nur ein passives Element, sondern arbeitet aktiv mit – dank Foveros Direct 3D, wie im kommenden Abschnitt noch etwas näher erläutert wird.

Im Base Tile sind nicht nur die vier Speichercontroller zu finden, sondern zusätzlich auch noch beachtliche 192 MByte L3-Cache – das erinnert auf den bei AMDs X3D-CPUs inzwischen untergeschobenen 3D V-Cache.

Dank dreifacher Ausführung kommt die CPU am Ende so auf 576 MByte L3-Cache und bietet 12 Speicherkanäle. Untereinander kommunizieren die CPU-Dies auf den Base-Tiles weiterhin via EMIB, Intels eigener Bridge-Technologie.

Apropos Speichercontroller: Dieser kann über insgesamt zwölf Kanäle DDR5-8000 ansprechen. MR-DIMM-Support, wie er bei den großen P-Core-Prozessoren verfügbar ist, gibt es auch für Clearwater Forest wie bereits mit Sierra Forest nicht.

Der bekannte I/O-Tile sorgt für Kompatibilität mit Birch Stream

Für die Kommunikation nach außen sorgen die I/O-Tiles. Zwei davon sind verbaut, je einer an jeder Längsseite der CPU. Die bereits angesprochene Besonderheit: Es sind genau die gleichen wie bei Granite Rapids und Sierra Forest. Genau deshalb werden diese Lösungen vollständig kompatibel zu der bisherigen AP-Plattform im großen Sockel LGA 7529 sein. Erste kompatible Server hatte Intel bereits in Arizona ausgestellt.

Foveros Direct 3D mit Hybrid Bonding feiert sein Debüt

Mit dem neuen Serverchip feiert Intels neues Packaging sein Debüt. Der Name Foveros Direct 3D bezieht sich auf die direkte Verbindung zwischen zwei aktiven Chips in der dritten Dimension, also der Höhe. Es ist damit quasi das Gegenstück zu TSMCs 3D-Stacking, welches beispielsweise für die AMD Ryzen X3D genutzt wird. Dort wird ein aktiver Cache-Die unterhalb des eigentlichen CPU-Dies „geschoben“ und miteinander verdrahtet.

Ähnlich ist das nun bei Intel. Auch hier wird ein Die (Chip) mit ganz großem Cache, aber zusätzlich auch den darunterliegenden Speichercontrollern der eigentlichen CPU-Kerne platziert und mittels Hybrid Bonding, wie die Technik heißt, verdrahtet.

Der verdrahtete Base Tile kann bei Intel aber noch mehr. Da die neuen CPU-Kerne in Intel 18A Power Delivery von der Rückseite erhalten, sind im Base Tile auch die stromführenden Leitungen zu finden. Über ein Mesh kann zudem jeder Kern mit dem anderen sprechen und auf den gesamten L3-Cache zugreifen.

Foveros Direct ist erst der Auftakt. Schnell sollen in den kommenden Jahren Verbesserungen Einzug halten, das Stapeln noch weiter optimiert werden. In Zukunft wird es dann auch einen „Core X3D“ geben, vermutlich so gelöst aber erst mit Intel Titan Lake. Intel Nova Lake mit bLCC ( big Last Level Cache) packt Ende 2026 diesen wiederum als insgesamt größerer Chip direkt neben die CPU-Kerne. Dies hat den Vorteil, dass er direkt anliegt und statt 32 oder 36 MByte nun eben 144 MByte groß ist. Der Nachteil ist, dass der CPU-Die so viel größer wird. Da Intel 18A bis dahin aber noch fast ein Jahr reifen kann, dürfte die Ausbeute dafür zufriedenstellend sein.

Ersteindruck

Intel Clearwater Forest hat zwei große Aufgaben zu erfüllen: Die Architektur ist nicht nur die zweite Phase des Experiments mit einem E-Core-Only-Prozessor, auch führt sie neue Fertigungstechnologien und neue Packaging-Optionen ein. Auf die letztgenannte werden viele weitere Generation an Prozessoren folgen, das erste Produkt aus der Serienfertigung ebnet den Weg.

Was den Prozessor und seine Leistung angeht, dahinter bleiben im Rahmen der Vorstellung einige Fragezeichen stehen. Denn die Vergleiche, die Intel in Arizona zwischen Clearwater Forest mit 288 Kernen und Sierra Forest mit 144 Kernen anstellte, waren Augenwischerei.

Denn Sierra Forest-AP, also die Version, die ebenfalls schon 288 Kerne im gleichen Sockel wie nun Clearwater Forest bietet und auch bereits 12 Speicherkanäle anspricht, unterschlug das Unternehmen vor Ort. In der Tat wollte diese CPU zuletzt kaum ein Kunde einsetzen, sie griffen lieber zu Granite Rapids. Es gibt den Prozessor aber nun einmal, zwar nicht in Großserie und nur für gewissen Kunden, aber sie existiert.

Immerhin hat Intel wenige Stunden vor der Veröffentlichung mit einer zusätzlichen Folie gegensteuerte. Viele der genannten Leistungszuwächse fallen in diesem Duell natürlich geringer aus.

Nichtsdestoweniger sind die einzelnen Darkmont-E-Cores deutlich stärker als zuletzt, daran besteht kein Zweifel. Auch schnellerer Speicher und der größere L3-Cache helfen ungemein. Und mit 450 Watt gegen 500 Watt positioniert sich der Neuling auch etwas effizienter.

Ob Clearwater Forest damit Erfolg haben wird, wird sich aber erst ab Mitte 2026 zeigen. Offiziell ist die finale Vorstellung für das erste Halbjahr 2026 geplant. Der Tenor auf der Intel-Veranstaltung war jedoch, dass es wohl eher gen Ende diese Zeitraums tendiert. So richtig überzeugen konnte das Paket deshalb im Ersteindruck nicht.

ComputerBase hat Informationen zu diesem Artikel von Intel im Vorfeld und im Rahmen einer Veranstaltung des Herstellers in Chandler, Arizona, unter NDA erhalten. Die Kosten für Anreise, Abreise und vier Hotelübernachtungen wurden von dem Unternehmen getragen. Eine Einflussnahme des Herstellers auf die oder eine Verpflichtung zur Berichterstattung bestand nicht. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.

Apps & Mobile Entwicklung

Dieses beliebte Modell gibt es jetzt günstiger

Auch am zweiten Prime Day 2025 dürfen Angebote von Soundcore nicht fehlen. Hersteller Anker hat sich mit den bekannten Bluetooth-Lautsprechern und Kopfhörern bereits auf dem Markt etabliert und kann vor allem mit einem ausgezeichneten Preis-Leistungs-Verhältnis glänzen. Das gilt auch für den kabellosen Lautsprecher Motion Boom Plus, der Ihr aktuell mit einem satten Rabatt abgreifen könnt.

Auch am zweiten Prime Day in diesem Jahr gibt es wieder zahlreiche Deals zu entdecken. Wie üblich ist auch Anker mit den Soundcore-Produkten am Start und bietet verschiedene Kopfhörer oder Bluetooth-Lautsprecher zu echten Kracher-Preisen an. Das gilt auch für den Soundcore Motion Boom Plus. Diesen bekommt Ihr jetzt zum Bestpreis bei Amazon.

Starker Sound und fetter Bass

Der Bluetooth-Lautsprecher (Kaufberatung) erinnert vom Design stark an einen Ghettoblaster aus den 90er-Jahren – nur eben in einer deutlich kleineren Version. Ein Haltegriff auf der Oberseite ermöglicht den einfachen Transport des knapp 2 kg schweren Speakers. Satte 80 W Gesamtleistung erzeugt das Gerät über seine zwei 30-W-Tieftöner und zwei 10-W-Hochtöner. Hinzu kommt die BassUp-Technologie, die laut Hersteller für einen klar hörbaren Bass sorgen soll.

Ein integrierter USB-C-Port ermöglicht zudem das Aufladen Eures Smartphones, wodurch der soundcore Motion Boom Plus zu einer ziemlich wuchtigen Powerbank mutieren kann. Eines der Highlights ist jedoch die versprochene Akkulaufzeit von bis zu 20 Stunden. Diese hängt natürlich stark von der Nutzung ab, allerdings sollte die nächste Party damit problemlos überstanden werden. Über die App könnt Ihr zudem den Equalizer einstellen. Eine IP67-Zertifizierung gewährt zudem einen Schutz vor Staub und Wasser.

Soundcore Motion Boom für 60 Euro: Lohnt sich das?

Die unverbindliche Preisempfehlung der Musikbox liegt derzeit bei 136 Euro. Hier setzt Amazon den Rotstift an und streicht kurzerhand 34 Prozent. Dadurch zahlt Ihr nur noch 89,99 Euro. Laut Preisvergleich gibt es aktuell kein besseres Angebot im Netz. Falls Ihr also vorhabt Euch einen neuen Bluetooth-Lautsprecher anzuschaffen und wollt zudem nicht auf eine gute Leistung in Verbindung mit einem stabilen Design verzichten, solltet Ihr diesen Deal definitiv genauer unter die Lupe nehmen.

Was haltet Ihr von dem Angebot? Habt Ihr bereits Geräte von soundcore im Einsatz? Lasst es uns in den Kommetaren wissen!

Apps & Mobile Entwicklung

ComputerBase in den Reinräumen von Intels Fab 52

Heute wird Intels nagelneue Fab 52 offiziell eröffnet. Sie fertigt Intel Panther Lake (Details) und Clearwater Forest in Intel 18A – also in Großserie! Bis dahin war es ein beschwerlicher Weg; der Campus in Chandler, Arizona, hat schon so einiges durchgemacht, aber auch noch viel vor. ComputerBase hat sie im Bunny Suit besucht.

Zu Besuch in der Intel Fab 52

Alles andere als normal

Halbleiterhersteller lassen sich ungern in die Karten sehen, schon gar nicht in die neuesten Anlagen sollen Personen gelangen, die dort nicht hingehören. Selbst bei Intel werden die meisten Angestellten, auch wenn sie zum Teil schon Jahrzehnte dort arbeiten, eine Fab nie von innen sehen.

Für ausgewählte Medienvertreter gab es jetzt allerdings die berühmte Ausnahme, denn Intel will zeigen: Intel 18A läuft in Großserie an – eine Notbremse wie auf den letzten Metern bei Intel 20A gibt es dieses Mal nicht.

Konkret lud Intel Medienvertreter und Analysten in der vergangenen Woche nach Arizona in die Fab 52, die heute offiziell die Serienproduktion der Intel-18A-Chips für Panther Lake und Clearwater Forest aufnimmt.

Einblicke auch im Podcast-Format

Neben dem nachfolgenden Bericht hat sich Volker diese Woche gemeinsam mit Jan im Podcast über seinen Besuch in der Intel Fab 52 unterhalten. Wie es sich angefühlt hat, in den Bunny Suit zu steigen oder vom Werksleiter mitten im Reinraum den Schuh neu gebunden zu bekommen, gibt es in CB-Funk #139 ab Minute 39:10 zu hören.

Die Intel Fab 52

Intels Historie am Standort

Baubeginn der Fab 52 war 2021. Mit der Eröffnung heute sind letztlich rund vier Jahre vergangen, was für eine State-of-the-Art-Fab ein ziemlich normales Zeitfenster darstellt. Die Fabrik steht in Chandler, Arizona, quasi einem Vorort südlich von Phoenix. Intel ist dort bereits seit 1980 vertreten. 1990 ging es dann richtig los: Fab 12 als hochmoderne Anlage wurde an der Ocotillo Site (OC), wie der Campus heißt, errichtet, Fab 22 folgte rasch und wurde bereits 1996 eröffnet. Anfang der 2000er gab es die nächste Erweiterung: Fab 32. Danach wurde es ruhiger.

Fab 42 war als Riesenprojekt ab 2011 geplant, dann jedoch aufgrund der schwachen wirtschaftlichen Lage nicht ausgerüstet worden. 2017 holte Intel den Bau wieder aus dem Winterschlaf und stellte ihn für 7 Milliarden US-Dollar fertig. Unter Pat Gelsinger und dem neuen Foundry-Ansatz kamen 2021 dann die Pläne für Fab 52 und 62 hinzu.

Heute baut Fab 42 Intel-7-Lösungen (10 nm), Fab 52 nebenan nun die neuen 18A-Chips. Und Fab 62 ist im Rohbau fertig, aber noch nicht ausgerüstet. Sollten alle Module, wie die Ausrüstungsphasen bei Intel heißen, hier aber einmal installiert werden, dann wäre Fab 62 noch größer als die Fab 52, erklärte Intel auf Nachfrage von ComputerBase. Doch dafür braucht es wohl echte Foundry-Kundschaft – also externe Kunden.

Ein Rundgang zum Auftakt

Der Auftakt der Tour war eine Runde um das Gelände. Das gibt einen guten Überblick, wie sich Intel hier entwickelt hat, aber auch, wie groß Halbleiterfabriken in den letzten Jahren geworden sind. Fab 12 ist nach heutigen Maßstäben winzig, Fab 22 kaum größer. Fab 32 legte die Messlatte höher dann, Fab 42 ist schon ziemlich groß. Fab 52 und Fab 62 sind jedoch noch einmal ein ganz anderes Kaliber. Für neue Maschinen mussten sie anders aufgebaut werden und sind daher auch höher.

Ein von Intel bereitgestelltes Drohnen-Video zeigt die verbundene Anlage aus Fab 42, Fab 52 und zukünftiger Fab 62.

100 Megawatt sind möglich

Auch die Stromversorgung des Komplexes, die südöstlich der Fab 62 liegt, wurde zuletzt auf 100 Megawatt aufgewertet – denn hochmoderne Lithographiesysteme benötigen jede Menge Energie. Und natürlich auch Wasser. Eine große Aufbereitungsanlage steht auf der anderen Seite des Komplexes.

Intel betont, dass man in Arizona nach den neuesten Bauten „water positive“ sei. Dies bedeute nicht, dass Intel wenig Wasser verbraucht, man jedoch der Community durch zusätzliche Projekte unter dem Strich aber mehr Wasser zurückgibt als entnimmt.

Die gesamten Investitionen von Intel in Arizona liegen bisher bei rund 50 Milliarden US-Dollar, erklärte das Unternehmen. Das Unternehmen ist vor allem auf den letzten Meilenstein so stolz, dass es diese letzte Errungenschaft auch teilen möchte. In Form kleiner Gruppen aus Personen in weißen Anzügen, den sogenannten „Bunny Suits“, ging es deshalb nach dem Rundgang in die heiligsten Hallen.

Im Bunny Suit durch Fab 42 und Fab 52

Für Besucher einer dieser hochmodernen Anlagen, sofern sie überhaupt zugelassen sind, gibt es diverse strikte Auflagen. Das oberste Ziel dabei ist, Verunreinigungen im Reinraum zu vermeiden.

Frisch geduscht ins Hasenkostüm

Frisch geduscht sollte man sein, aber das war es dann auch: Nichts in die Haare, nichts ins Gesicht, kein Duft oder Parfüm – Aerosole gilt es zu vermeiden. Dress Code: Geschlossene Schuhe und eine lockere Hose, dazu ein Shirt – mehr nicht. Denn über all das kommt der berühmte Bunny Suit – und darunter ist es warm.

Da der Laie mit dessen Anlegen total überfordert wäre beziehungsweise der Prozess viel zu lange dauern würde, bekam jeder Journalist vor Ort eine Anzieh-Hilfe. Der Autor war zwar bereits in den Fabs in Kyriat Gat, Israel, und den Produktionsstätten in Malaysia, aber mit Jahren Abstand halfen diese Erfahrungen in der Praxis in Arizona dann letztlich nicht mehr.

Im Aufenthaltsraum außerhalb der Reinräume konnten sich die Besucher aber schon einmal mit den Dingen vertraut machen.

20 Minuten durch einen Parcours

Denn der Zeitplan war eng gesteckt. Kleine Gruppen von je sechs bis acht Personen durften einen vorgegebenen und abgesteckten Parcours ablaufen und dabei die Fabrik im regulären Arbeitsprozess nicht behindern. Um Notizen zu ermöglichen, stellt Intel spezielle Notizblöcke zur Verfügung: Reinraum abgesegnet! Eigene Fotos oder Videos waren nicht erlaubt – aber das ist wenig überraschend. Denn eine bessere Fertigung in Serienproduktion gibt es aktuell nicht, sagt Intel – und hat damit durchaus recht: TSMCs neuer 2-nm-Prozess ist noch nicht in Serie, bis dahin dürfte Intel 18A die beste Lösung sein.

Die Gruppe machte sich nach dem Einkleiden durch einen kleineren Supportbereich auf in die Fab 42, die über einen Zugangstunnel direkt mit Fab 52 verbunden ist. Fab 42 fertigt Chips mit Intel 7 (10 nm). Hier sind unter anderem ASMLs DUV-Systeme sowie unzählige zusätzliche Tools und Gerätschaften zu sehen, deren Namen aber nicht genannt werden dürfen – das wollen sowohl die Partner als auch Intel nicht. Schon nach wenigen Minuten ist aber beinahe jeder Name der großen westlichen Fabrikausrüster zu sehen gewesen. ASMLs DUV-System ist das beste im Markt, wenn Chips ohne EUV gefertigt werden müssen. Genau das macht Fab 42.

Das an der Decke verbaute Transportsystem, welches die Wafer umherfährt, ist komplett über alle fünf Fabs verbunden. Das ist nicht unwichtig, denn die allerbesten Fertigungsschritte werden nicht überall und bei jedem Produkt und in allen Layern benötigt, also können diese auch woanders hinfahren und dort fertiggestellt werden.

Der heilige Gral: der EUV-Belichter

Endlich in Fab 52 angekommen, geht der Weg direkt zum wichtigsten Gerät der Anlage: einem EUV-System von ASML. Dies ist der aktuell modernste und teuerste EUV-Belichter des niederländischen Fabrikausrüsters, hier fertigt er aktuell die Compute-Tiles von Panther Lake und bald auch Clearwater Forest. Beeindruckend ist dabei einmal mehr die schiere Größe dieses einzelnen Systems, der DUV-Belichter in der Fab zuvor fällt deutlich kleiner und kompakter aus. Wie üblich sieht man dabei auch nur den einen Teil, die ganzen zusätzlichen Gerätschaften beispielsweise darunter eben nicht.

ASMLs EUV-Systeme können wie die DUV-Belichter stets auf den letzten Stand aufgerüstet werden. Jeder Kunde ist also bestrebt, dies auch schnellstmöglich zu tun, da damit einher oft viele Verbesserungen ins Spiel gelangen und der Durchsatz erhöht sowie die Fehlerquote und die Downtime reduziert werden.

Selbst wollte Intel nicht sagen, wie viele dieser Belichtungssysteme in Fab 52 verbaut sind. Die optimistischen Schätzungen gehen von einem Dutzend Systemen oder mehr aus, da vieles intern symmetrisch respektive dann auch gespiegelt aufgebaut ist.

Jedes dieser Systeme schafft die Belichtung von 200 bis 220 300-mm-Wafern die Stunde. Weil oftmals Schritte mehrfach vollzogen werden, ist die einfache Hochrechnung über x Systeme dann jedoch nicht so einfach, um in Richtung monatliche Kapazität hochzurechnen. Letzte Gerüchte, die aber nur von 1.000 bis 5.000 Wafern im Monat sprachen, klingen jedoch eher zu niedrig, wenn die Fab wie geplant arbeitet.

Nachdem die Medienvertreter ihr Programm abgeschlossen hatten, überzeugte sich Anfang Oktober auch Intels CEO Lip-Bu Tan im Bunny Suit von den Arbeiten in der Fab und positioniert sich vor dem EUV-System als dann auch vor der Anlage mit einem Intel-18A-Wafer.

Kein (interessantes) Packaging vor Ort

Was Fab 52 nicht macht, ist das Packaging, also das Verbinden unterschiedlicher Chips auf einem Träger. Natürlich werden vor Ort einige erste Tests gemacht, doch das komplette Die-Sort, Prep und Co geschieht dann in New Mexico.

Unterm Strich ist ein Packaging-Werk das viel interessantere für einen Besuch, denn während in der Fab 52 primär „nur graue Kästen“ angesehen werden konnten, konnte vor zwei Jahren in Malaysia der ganze Rest betrachtet werden – und das auch nicht nur in 20 Minuten, sondern über Stunden in mehreren Komplexen. Mehr Details zu diesen Schritten, die auch bei Panther Lake noch Bestand haben, gibt es im Bericht aus Malaysia:

- Vor-Ort-Besuch: Einblicke in Intels Test- und Packaging-Prozess in Malaysia

Intel 18A im Überblick

Mit RibbonFET und PowerVia

Eine bahnbrechende Neuerung bei Intel 18A ist zum Beispiel RibbonFET, wie Intel die Next-Gen-Fertigung rund um Gate all around (GAA) nennt. Das ist bei jedem Halbleiterhersteller aktuell das große Ding, das die nächste Dekade über Transistoren definieren wird. Oft auch Nanosheets genannt, sind diese extrem dünnen Fäden – 10.000 Sheets wären noch dünner als ein Blatt Papier – komplett umschlossen und ermöglichen so den perfekten Transistor. Daran wurde Jahrzehnte lang geforscht, nun gehen Samsung, Intel und TSMC hier nahezu im Gleichschritt in die Massenproduktion über.

Backside Power Delivery (BSPD) heißt bei Intel PowerVia. Intels eigene Umsetzung der Technologie soll sich dabei etwas vom Original unterscheiden, nicht nur der Name sei ein anderer. Die grundlegende Technik der rückseitigen Stromversorgung von Transistoren ist wiederum keine exklusive Entwicklung, sie steht bei jeder Firma auf der Roadmap. Intel ist hier jedoch am weitesten fortgeschritten, geht nun als erster in Serienproduktion.

Bisher machen sich Strom- und Signalleitungen auf der Vorderseite eines Chips gegenseitig den Platz streitig, behindern sich mitunter sogar. Die Trennung von beiden bietet mehrere Vorteile sowohl in Richtung Skalierung als auch Effizienz: Signalleitungen haben mehr Platz, während sich auf der Rückseite die Stromzufuhr austoben kann. Ein Nachteil ist jedoch das Handling der Wafer, die in der Produktion gedreht werden müssen.

Da Intel beide neuen Technologien auf Intel 18A optimiert hat, verspricht das Unternehmen diverse Vorteile gleich zu Beginn. Denn das Herauslösen der Stromleitungen vereinfacht am Ende den Produktionsprozess sogar so weit, dass deutlich weniger Masken und Schritte nötig sind, wenn es mit einem klassischen Prozess verglichen würde.

Am Ende soll Intel 18A mit den beiden neuen Technologien Vorteile sowohl bei der Leistung, dem Stromverbrauch und natürlich dem Flächenbedarf bieten.

Höherer Yield als in der Vergangenheit

Intel gibt an, dass die Ausbeute von Intel 18A zum Start besser oder auf vergleichbarem Niveau liegt mit dem, was in den letzten 15 Jahren bei Intel neu gefertigt wurde.

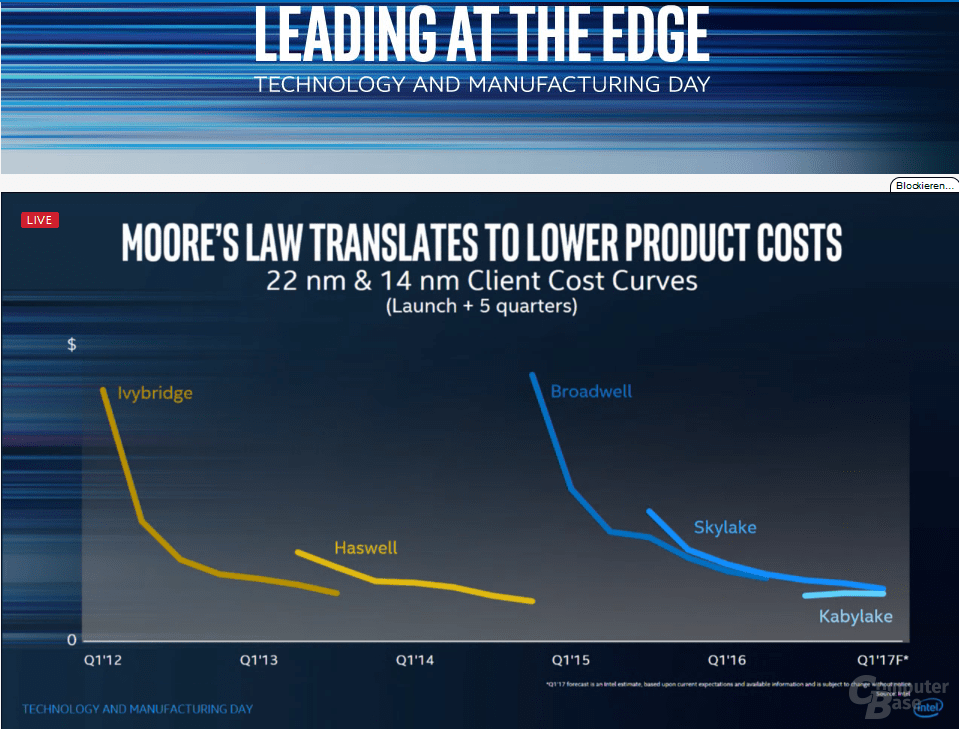

Was das absolut bedeutet, ist allerdings nicht klar, denn wie in den letzten Jahren bekannt wurde, lief eigentlich keiner der Prozesse zum Auftakt wirklich rund: 10 nm war ein vollkommener Fehlschlag, 14 nm mit Broadwell war zum Start ein Desaster und selbst 22 nm mit der Einführung von FinFETs im Jahr 2012 mit Ivy Bridge startete nicht rund. Im Jahr 2017 hatte das Intel im Rahmen einer Präsentation selbst einmal so bestätigt. Am Ende sind aber auch nicht die ersten Wochen entscheidend, sondern wie schnell der Prozess reift. Das wird sich die kommenden Monate zeigen.

Für weitere Details hat Intel zum Start der Fertigung auch noch einmal viele Informationen in einem Video zusammengestellt.

Intel 18A ist nur für Intel

Am Ende ist und bleibt Intel 18A aber ein Prozess erst einmal ausschließlich für Intel. Denn für Intel wurde dieser entwickelt und optimiert, nicht für externe Kundschaft. Deshalb konnte Intel Foundry bisher auch keinen Großkunden gewinnen – ihnen stehen schlichtweg nicht die Tools zur Verfügung, um eigene Chips auf Intel 18A auszulegen.

Für die nächste große Stufe, Intel 14A, wird das andersherum angegangen. Hier soll ein universeller Prozess entstehen, Kunden können diesen dann mit Intel Foundry zusammen optimieren.

Ob das funktioniert, werden die kommenden Jahre zeigen. Platz für zusätzliche EUV-Belichter hat Intel jedenfalls, und das nicht nur in Arizona. Schließlich baut Intel – aktuell zwar nur langsam – einen großen Komplex in Ohio. Ob und wann dieser fertig, oder am Ende komplett kassiert wird, hängt am Erfolg von Intel 14A bei externen Kunden ab, aber auch dem Grundstein, der nun mit Intel 18A gelegt wird.

ComputerBase hat Informationen zu diesem Artikel von Intel im Vorfeld und im Rahmen einer Veranstaltung des Herstellers in Chandler, Arizona, unter NDA erhalten. Die Kosten für Anreise, Abreise und vier Hotelübernachtungen wurden von dem Unternehmen getragen. Eine Einflussnahme des Herstellers auf die oder eine Verpflichtung zur Berichterstattung bestand nicht. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.

-

UX/UI & Webdesignvor 2 Monaten

UX/UI & Webdesignvor 2 MonatenDer ultimative Guide für eine unvergessliche Customer Experience

-

UX/UI & Webdesignvor 1 Monat

UX/UI & Webdesignvor 1 MonatAdobe Firefly Boards › PAGE online

-

Social Mediavor 2 Monaten

Social Mediavor 2 MonatenRelatable, relevant, viral? Wer heute auf Social Media zum Vorbild wird – und warum das für Marken (k)eine gute Nachricht ist

-

Entwicklung & Codevor 2 Monaten

Entwicklung & Codevor 2 MonatenPosit stellt Positron vor: Neue IDE für Data Science mit Python und R

-

Entwicklung & Codevor 1 Monat

Entwicklung & Codevor 1 MonatEventSourcingDB 1.1 bietet flexiblere Konsistenzsteuerung und signierte Events

-

UX/UI & Webdesignvor 3 Wochen

UX/UI & Webdesignvor 3 WochenFake It Untlil You Make It? Trifft diese Kampagne den Nerv der Zeit? › PAGE online

-

Apps & Mobile Entwicklungvor 3 Monaten

Apps & Mobile Entwicklungvor 3 MonatenFirefox-Update 141.0: KI-gestützte Tab‑Gruppen und Einheitenumrechner kommen

-

Online Marketing & SEOvor 2 Monaten

Online Marketing & SEOvor 2 MonatenSo baut Googles NotebookLM aus deinen Notizen KI‑Diashows