Apps & Mobile Entwicklung

Benchmarks zu MacBook Pro M5 Max und MacBook Air M5

In der vergangenen Woche hatte Apple das MacBook Air mit M5 sowie das MacBook Pro mit M5 und M5 Max vorgestellt. ComputerBase hat beide Serien von Apple zum Testen erhalten, zum Fall des Test-Embargos gibt es erste Einblicke in die Testergebnisse bezüglich einer Leistung und Akkulaufzeiten mit M5 und M5 Max.

Die Testmuster

Das MacBook Pro 16“ mit M5 Max (18/40)

Das neue MacBook Pro in 14“ und 16“ Zoll (2026) steht ab sofort mit M5, M5 Pro und M5 Max zur Wahl, wobei es jeweils auch noch verschiedene Ausbaustufen des SoC gibt.

Apple hat ComputerBase ein MacBook Pro 16“ mit M5 Max mit 18 CPU-Kernen und 40 GPU-Clustern zur Verfügung gestellt – das entspricht der größten Ausbaustufe des SoC (mit 128 GB + 4 TB, Space Schwarz, Nanotextur; UVP: 7.179 Euro). Wer noch mehr Geld ausgeben möchte, kann im Konfigurator lediglich noch 8 statt 4 TB SSD-Speicherplatz wählen, der Rest ist schon „maxed out“.

- MacBook Pro M5, M5 Pro & M5 Max: Von 1.899 bis 8.679 Euro hat Apple alles im Angebot

Das MacBook Air 15“ mit M5 (10/10)

Das neue MacBook Air (2026) gibt es nur mit M5, in der Version in 15 Zoll ist immer der ganze Chip mit 10 CPU-Kernen und 10 GPU-Shader-Clustern aktiv. Dieses Modell hat Apple der Redaktion zum Testen gestellt (mit 32 GB + 2 TB in Himmelblau; UVP: 2.749 Euro).

Im parallel aktualisierten 13-Zoll-Modell haben Käufer die Wahl zwischen der 10/10-Kern-Variante und einem Modell mit 10 CPU-Kernen und 8 GPU-Shader-Clustern. Eine Besonderheit bleibt dem Air dabei auch in der Generation mit Apple Silicon M5 erhalten: das lüfterlose Kühlsystem.

- Neues MacBook Air mit M5: Schneller, mit mehr Speicher, aber auch 100 Euro teurer

Erste Benchmarks

Alle von Apple in der vergangenen Woche vorgestellten neuen Produkte (MacBook Pro M5 Pro/M5 Max, MacBook Air M5 & MacBook Neo sowie iPhone 17e und iPad Air M4) kommen am 11. März auf den Markt, vorbestellbar sind sie schon seit dem 4. März. Die Test-Embargos fielen hingegen schon heute.

Krankheitsbedingt (und weil die Geräte erst Donnerstagnachmittag zugestellt wurden), gibt es heute noch keine umfassenden Tests, aber einen ersten Eindruck der Leistungsfähigkeit des neuen M5 Max und des Tempos des M5 im passiv gekühlten MacBook Air 15“ – denn den M5 hatte ComputerBase schon im MacBook Pro 14“ mit M5 im Test.

Ein Überblick zur Einordnung

Die nachfolgende Tabelle stellt alle M-SoCs neben dem M3 noch einmal kompakt gegenüber, abgebildet ist immer nur die größte Ausbaustufe – in den nachfolgenden Benchmarks kamen aber auch nur diese Varianten zum Einsatz.

M5, M5 Pro und M5 Max setzen erstmals auf „Super Cores“, die noch oberhalb der Performance-Cores angesiedelt sind. „Super Cores“ lautet Apples neue (und beim M5 jetzt im Nachgang eingeführte) Bezeichnung für die schnellsten Kerne. Darunter gibt es beim M5 die bekannten Efficiency-Kerne, bei M5 Pro und M5 Max hingegen „neue Performance Kerne“; E-Cores bieten die beiden offiziell keine mehr.

- Apple Silicon: M5 Pro und M5 Max sind Dual-Die-CPUs in 3 nm ohne E-Cores

CPU-Leistung (Single/Multi)

Alle M5-Derivate haben dieselben schnellsten Kerne: die neuen „Super Cores“. M5 im MacBook Pro 14“, M5 Max im MacBook Pro 16“ und M5 im MacBook Air 15“ setzen sich auf dieser Basis auch geschlossen an die Spitze. Dem M5 im MacBook Air 15“ gelingt das allerdings vorrangig dank Cinebench, denn im Geekbench liegt das Air leicht zurück und in WebXPRT (nicht zu 100 %, aber überwiegend ein Single-Core-Test) ziehen auch ein paar M4 vorbei. Im Durchschnitt liegt M5 aber geschlossen in Front.

In Multi-Core-Lasten setzt sich der neue M5 Max mit 18 CPU-Kernen, darunter 6 „Super Cores“ und 12 Performance-Cores, von der hausinternen Konkurrenz ab. Der M4 Pro im Mac Mini wird im Durchschnitt um 28 Prozent geschlagen. In Affinity Foto sind es sogar 52 Prozent, doch in Cinebench 2024 gibt es sogar nur einen Gleichstand. Und nicht zu vergessen: Über dem M4 Pro gibt es auch noch einen M4 Max mit zwei zusätzlichen Performance-Kernen. Doch auch gegenüber diesem Modell dürften deutlich über zehn Prozent Zuwachs in der Leistung möglich sein – bei gleichem Fertigungsprozess, was nicht vergessen werden darf.

Mit Blick auf das neue und das alte MacBook Air sowie das MacBook Pro mit M5-SoC zeigt sich ein Leistungszuwachs von M4 zu M5 im Air, aber der erwartete Leistungsnachteil des M5 im Air gegenüber dem aktiv gekühlten M5 im MacBook Pro. Je länger die Last, desto deutlich kann dieser ausfallen: 30 Prozent Rückstand für das Air sind bei Dauerlast realistisch.

GPU-Leistung (Compute)

In den GPU-Compute-Benchmarks sieht die Leistung des M5 Max mit 40 Shader-Clustern beeindruckend aus und sie ist es auch. Der Vorsprung gegenüber dem M4 Pro erzählt in diesem Fall aber wirklich nur die halbe Geschichte, denn es gab auch einen M4 Max mit doppelt so starker GPU und in neuer Generation gibt es auch einen M5 Pro mit 20-Shader-Cluster-GPU. Aber auch ohne die beiden im Benchmark zu haben, wird deutlich: 40 Shader-Cluster auf basis der M5-GPU-Architektur sind sehr schnell.

Noch deutlicher als bei den CPU-Benchmarks wird bei den GPU-Compute-Ergebnissen am Ende aber klar, warum man mit Blick auf GPU Compute zu einem MacBook Pro mit M5 Pro oder M5 Max schielen könnte statt zum M5 zu greifen, dessen CPU für Alltagsaufgaben mit den schnellen Super Cores und zehn Kernen in Summe auch mehr als schnell genug ist.

Akkulaufzeit

Über das Wochenende schon abgeschlossen wurden die ersten Tests zur Akkulaufzeit: Das neue MacBook Air mit M5 erreicht dabei das Niveau des Vorgängers mit M4. Das MacBook Pro 16“ mit M5 Max hat keine direkten Vorgänger in der Testdatenbank der Redaktion, liegt mit sechzehneinhalb Stunden Laufzeit im Streaming-Test trotz großem 16-Zoll-Display aber weit vorne im Vergleich. Ein Nachteil durch den Wechsel der größeren und/oder leistungsfähigeren SoCs ist trotz gleicher Fertigung nicht zu erkennen.

Fazit

Ab sofort setzen auch MacBook Air und MacBook Pro in den Leistungsklassen Pro und Max auf die aktuellen M5-SoCs, während Chassis, Display, Anschlüsse, Tastatur und Kühlsystem gegenüber den Vorgängern der Generation M4 unangetastet bleiben.

Mit dem Wechsel setzen sich beide Serien jetzt geschlossen an die Spitze der Single-Core-Leistungs-Charts, denn der neue schnellste Kern von Apple – der „Super Core“ – ist am Ende genau das: Der derzeit schnellste CPU-Kern. M5 Pro und M5 Max wechseln gegenüber den Vorgängern zudem von E-Cores auf „neue Performance-Kerne“, was die Leistung auch in Multi-Core-Lasten weiter ansteigen lässt. 10+ Prozent im direkten Vergleich sind möglich, was aber auch zeigt, dass die neuen „Performance Cores“ den alten E-Cores näher stehen als den neuen Super Cores – andernfalls müsste die Leistung noch stärker steigen.

Einen größeren Schritt nach vorne macht auch die GPU, die in M5 Pro und M5 Max 1:1 die bereits vom M5 bekannte Architektur übernommen hat. Gegenüber M4 Pro und M4 Max sind trotz gleicher Anzahl an Shader-Clustern damit teils deutliche Zuwächse zu erzielen.

Auch das passiv gekühlte MacBook Air profitiert dabei vom Einsatz des M5: Trotz mutmaßlich – aber noch nicht per Messung bestätigt – gleichem TDP-Korsett und gleicher Fertigung sind Leistungszuwächse von M4 zu M5 zu verzeichnen, bei GPU Compute sind sie sogar sehr deutlich – das war von M4 zu M5 im MacBook Pro auch schon der Fall. Und die höhere Leistung gibt es im Air immer noch geräuschlos.

Die Leistung des M5 Max im MacBook Pro 16“ es im Leistungs-Modus hingegen nicht, aber das Kühlsystem dreht sehr konstant und es ist im Ende „nur“ Luftrauschen zu hören. Auch dauert es gut 40 Sekunden, bevor die Lüfter überhaupt anfangen hoch zu drehen, kurze Lastspitzen bringen auch das neue MacBook Pro mit M5 Max nicht aus der Ruhe.

Display, Chassis, Touchpad und Tastatur wurden in diesem Artikel nicht erneut gesondert beachtet, dann diese Aspekte sind gegenüber den Vorgängern unangetastet geblieben und liegen weiterhin auf einem extrem hohen Niveau. Das gilt auch für die Verarbeitung.

ComputerBase wurden das MacBook Air 15“ M5 und das MacBook Pro 16“ M5 Max leihweise von Apple unter NDA zum Testen zur Verfügung gestellt. Eine Einflussnahme des Herstellers auf den Test fand nicht statt, eine Verpflichtung zur Veröffentlichung bestand nicht. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.

Apps & Mobile Entwicklung

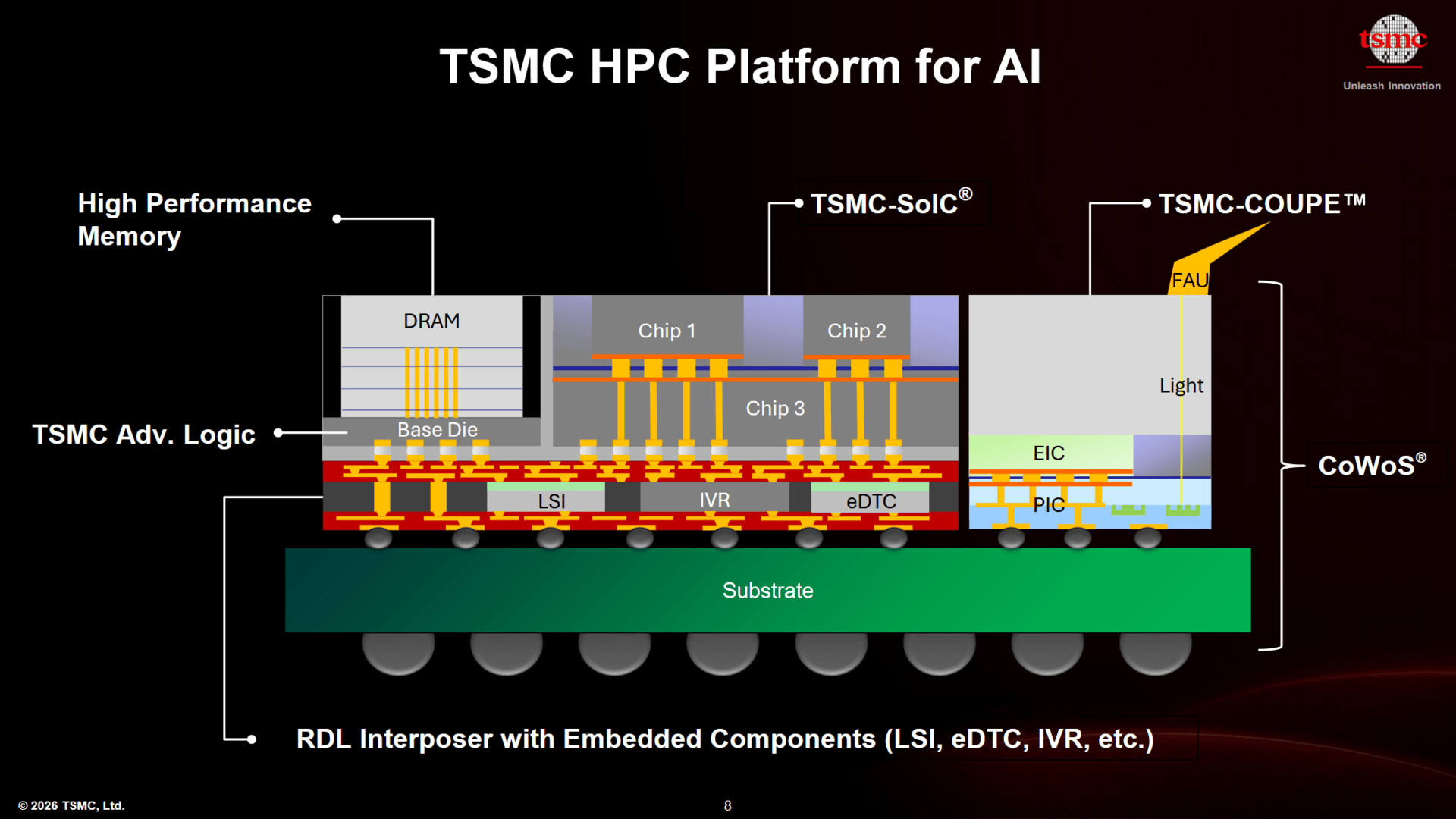

TSMC COUPE: Silicon Photonics im Substrat/Interposer setzt Konkurrenz zu

Eine größere Baustelle bei TSMC ist Silicon Photonics. Hier gibt es vielfältige Anbieter, die man mit kompletter Integration toppen will. Vor allem die Thematik rund um Co-Packaged Optics (CPO) hat das Unternehmen auf dem Schirm und könnte mit kompletter Integration via COUPE die Mitbewerber übertreffen.

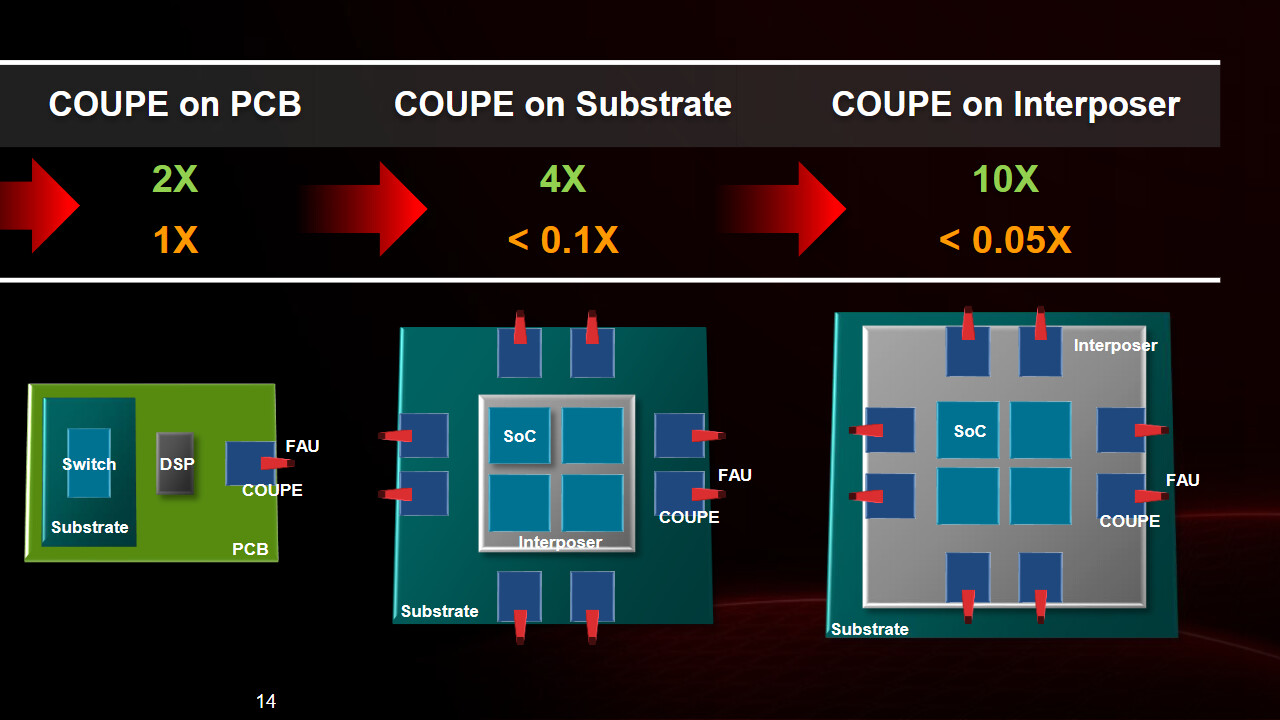

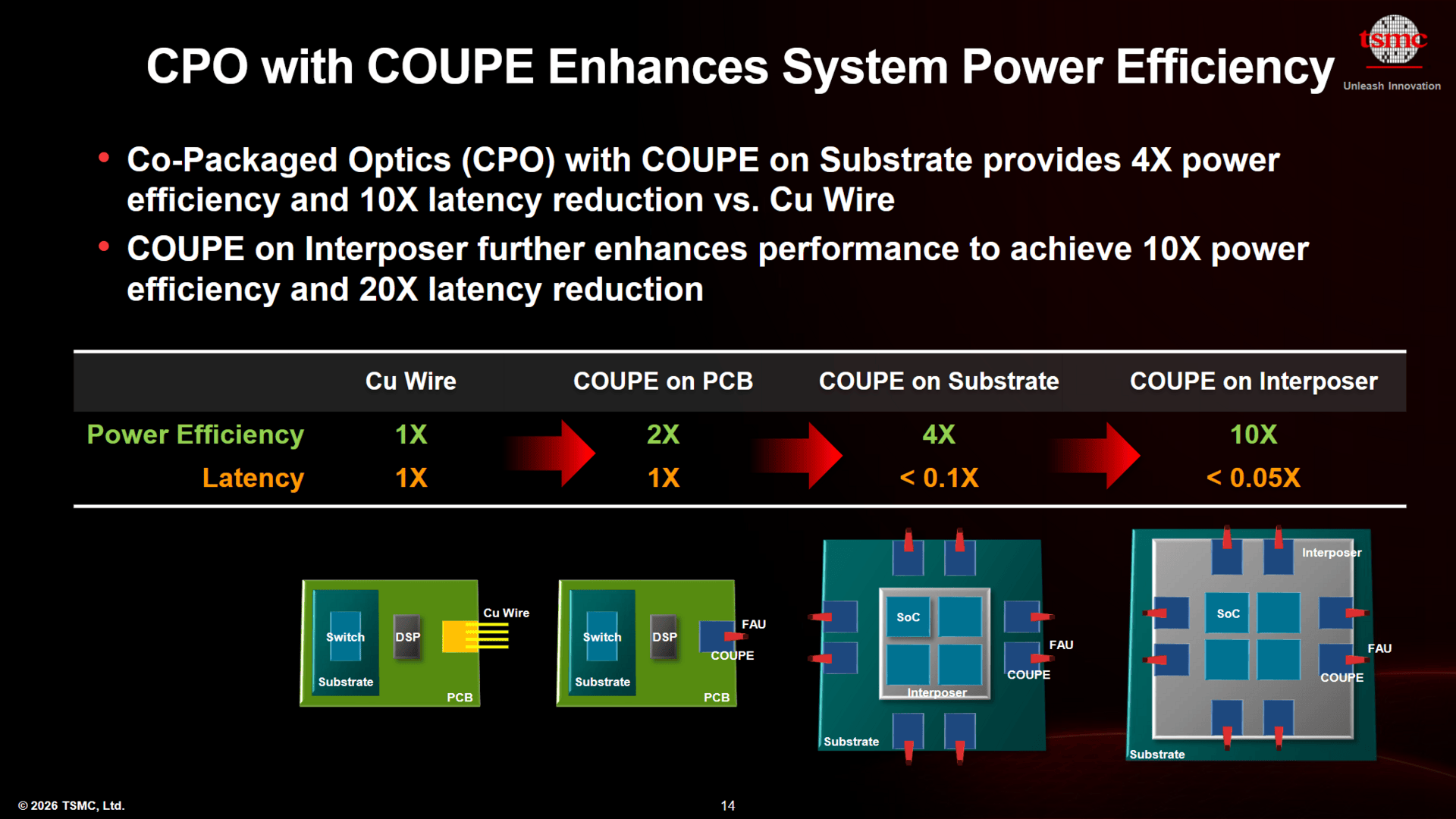

COUPE steht bei TSMC für Compact Universal Photonic Engine. Das Ziel ist es, ein echtes Co-Packaged-Optics-Paket zu schnüren und keine halben Lösungen, die es auf dem Weg dorthin aber definitiv geben wird. Denn in kleinen Schritten geht es bei CPO bisher voran, von der komplett losgelösten Lösung mit optischen Verbindungen im gleichen System, angeschlossen aber noch über ein Kupferkabel, über Silicon Photonics auf dem gleichen PCB, dann dem Substrat und Package bis schließlich zum Finale direkt im Interposer.

Die vom Konzern genannten Boni insbesondere für die komplette Integration am Ende, die laut eigener Aussage nur TSMC umsetzen könne, sind durchaus gewaltig. Die Latenzen sollen bereits bei der Lösung direkt im Substrat effektiv um den Faktor 10 gegenüber einer aktuellen Version „mit Kabel zum Board“ reduziert und die Effizienz verdoppelt werden. Die Basis dafür ist ein 200Gbps micro-ring modulator (MRM), die Serienproduktion hierfür beginnt im zweiten Halbjahr, erklärte TSMC auf Nachfrage. In der nächsten Generation direkt im Interposer sollen die weiteren Vorteile riesig ausfallen, sowohl beim Thema Latenz als auch bei der Effizienz.

TSMC war eher spät dran, was die gesamte Thematik angeht, und startete 2021 auf kleinem Niveau. Aber durch die fortschrittlichsten Technologien dürfte das Unternehmen in den kommenden Jahren den Mitbewerbern durchaus den Rang ablaufen. Erste ehemalige Partner bei Globalfoundries wie Ayar Labs sind nach zwei Generation zu TSMC gewechselt. Voran geht aber einmal mehr Nvidia, die groß auf COUPE schwenken werden. Die allererste Generation bei Nvidia kommt jedoch wohl nur zum Teil von TSMC, SPIL übernimmt hier Restarbeiten. Ähnlich ist es bei Broadcom, auch sie werden von SPIL zu TSMC wechseln.

AMD nutzt die Enosemi-Globalfoundries-Connection

Medial machte zuletzt die Rückkehr von AMD zu Globalfoundries die Runde, um Chips für Silicon Photonics zu beziehen. Was als Neuheit verkauft wurde, entspricht aber nur der halben Wahrheit. Denn im letzten Jahr hatte AMD das Unternehmen Enosemi übernommen, das wiederum Silicon-Photonics-Produkte auf Basis von Globalfoundries‘ IP entwickelt hat bei Globalfoundries ließ. Entsprechend kommen nun auch die darauf basierenden Lösungen von AMD von Globalfoundries.

Wie lange das so bleiben wird, ist jedoch abzuwarten. Da die Riesen Broadcom und Nvidia zu TSMC COUPE wechseln, könnte dies auch bei AMD in Zukunft der Fall sein. Denn vor allem des Gesamtpaket bei TSMC, fast alles aus einer Hand zu bekommen, dürfte neben den besten Fertigungstechnologien durchaus eine Rolle spielen.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

- TSMC Technology Symposium 2026

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Apps & Mobile Entwicklung

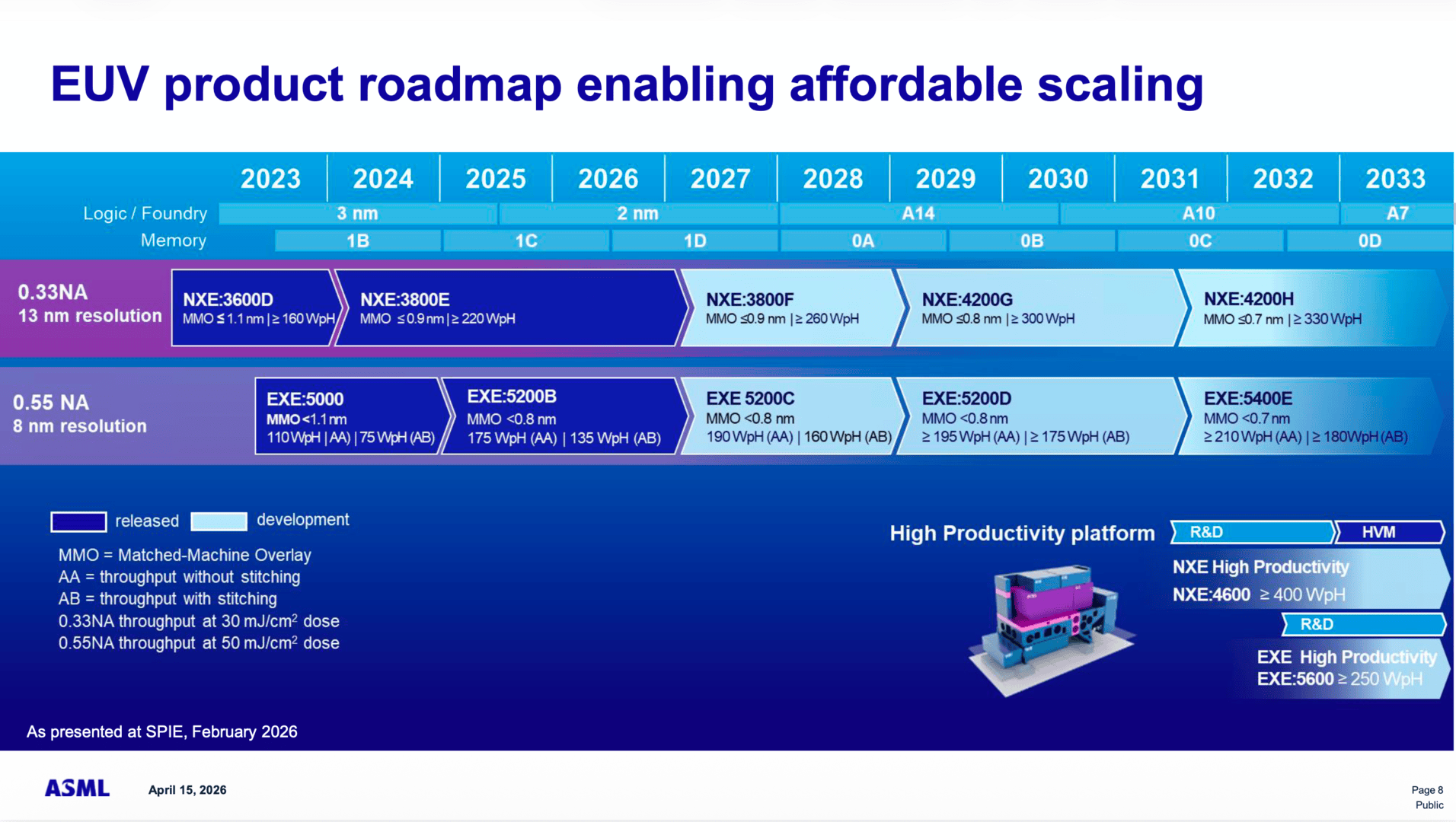

TSMC A13/A12-Fertigungsprozess: „1,2 nm“ mit Super Power Rail (ohne High-NA-EUV) ab 2029

Mit den Fertigungsprozessen A13 und A12 geht TSMC in die nächste Dekade. Kombiniert mit Super Power Rail wird A12 die Flaggschiffserie. Realisiert werden soll das alles weiterhin ohne High-NA-EUV, wie TSMC auf Rückfrage verdeutlicht. Die modernsten Low-NA-EUV-Belichter geben das alles problemlos her, erklärt der Hersteller.

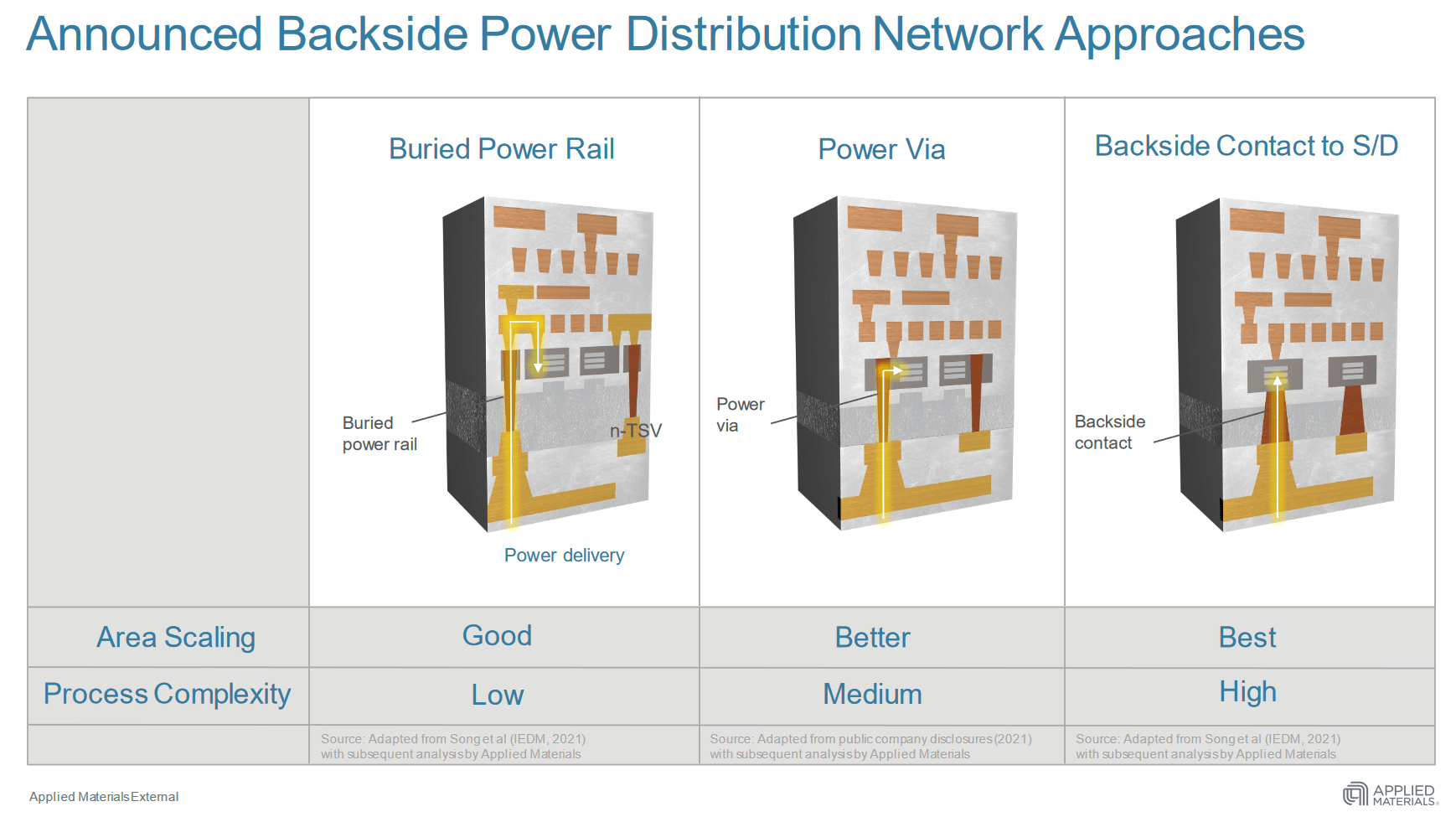

Dr. Kevin Zhang, Senior Vice President und Deputy Co-COO bei TSMC (und zuvor auch mal 12 Jahre bei Intel), erläuterte am Vorabend des Symposiums in den USA gegenüber der Presse die kommenden Entwicklungsschritte – mit extrem hohem technischen Verständnis. Auf dem Papier sieht es dabei so aus, als würden die Schritte kleiner werden. Dies ist aber der Zweigleisigkeit geschuldet, die TSMC derzeit fährt: Es gibt einen Standardprozess, und dann eine Linie, die auf BSPD, also die rückseitige Stromversorgung der Chips setzt.

Diese Zweigleisigkeit wird aktuell beim N2-Prozess eingeführt. Denn der kommende Fertigungsschritt A16 ist eigentlich N2 im Herzen, jedoch mit Backside Power Delivery (BSPN) ausgestattet. Der Nachfolger von N2 ohne BSPD wird der A14-Prozess, der Nachfolger von A16 mit BSPD letztlich deshalb A12. Die Basis dafür ist entsprechend der A14-Prozess mit Optimierungen. Auch hier setzt TSMC auf das sogenannte Super Power Rail (SPR), der besten Adaption von BSPD mit direktem rückseitigem Kontakt (die ganz rechte Lösung im Bild). Intel nutzt seit Panther Lake in Intel 18A die mittlere Variante mit Power VIAs.

A14-Prozess bekommt Shrink auf A13

Auf den A14-Prozess folgt im Standardverfahren binnen eines Jahres der A13-Prozess. Dies wiederum ist heutzutage vergleichbar mit dem Schritt von N3E auf N3P oder zukünftig N2 auf N2P. Mit einem optischen Shrink kann etwas Fläche von rund sechs Prozent eingespart werden, hier und da gibt es zudem minimale Vorteile durch den zeitlichen Versatz des Prozesses, sodass zusätzliche design-technology co-optimizations (DTCO) greifen und eine verbesserte Leistung und Effizienz versprechen. Da die Design-Tools und –Regeln identisch bleiben, können A14-Kunden schnell und direkt auf den angepassten Prozess schwenken.

High-NA-EUV bei TSMC weiterhin kein Thema

Stolz erklärte Zhang, dass TSMC auch bei den Prozessen für das Jahr 2029 auf High-NA werde verzichten können. Bisher hat das Unternehmen stets eine Möglichkeit gefunden, es wirtschaftlich mit den bestehenden Belichtern zu realisieren – auch heute monierte TSMC den sehr hohen Preis des rund 400 Millionen Euro teuren Systems. Die Entscheidung, wann High-NA bei TSMC zum Einsatz kommt, ist damit erneut vertagt worden, nachdem es im letzten Jahr bereits hieß, dass es vor 2029 nicht gebraucht wird.

Bei Intel könnten die ersten High-NA-Systeme eventuell ab 2027/2028 in der Produktion genutzt werden, aber auch hier klang es zuletzt danach, dass es eher später als früher wird. Ab dem Jahr 2030 dürften die High-NA-EUV-Systeme zudem einen deutlich höheren Reifegrad erreicht haben und so bestehende Low-NA-EUV-Systeme besser ergänzen können. Vermutlich tendiert TSMC erst dann zu einer Integration.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

- TSMC Technology Symposium 2026

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Apps & Mobile Entwicklung

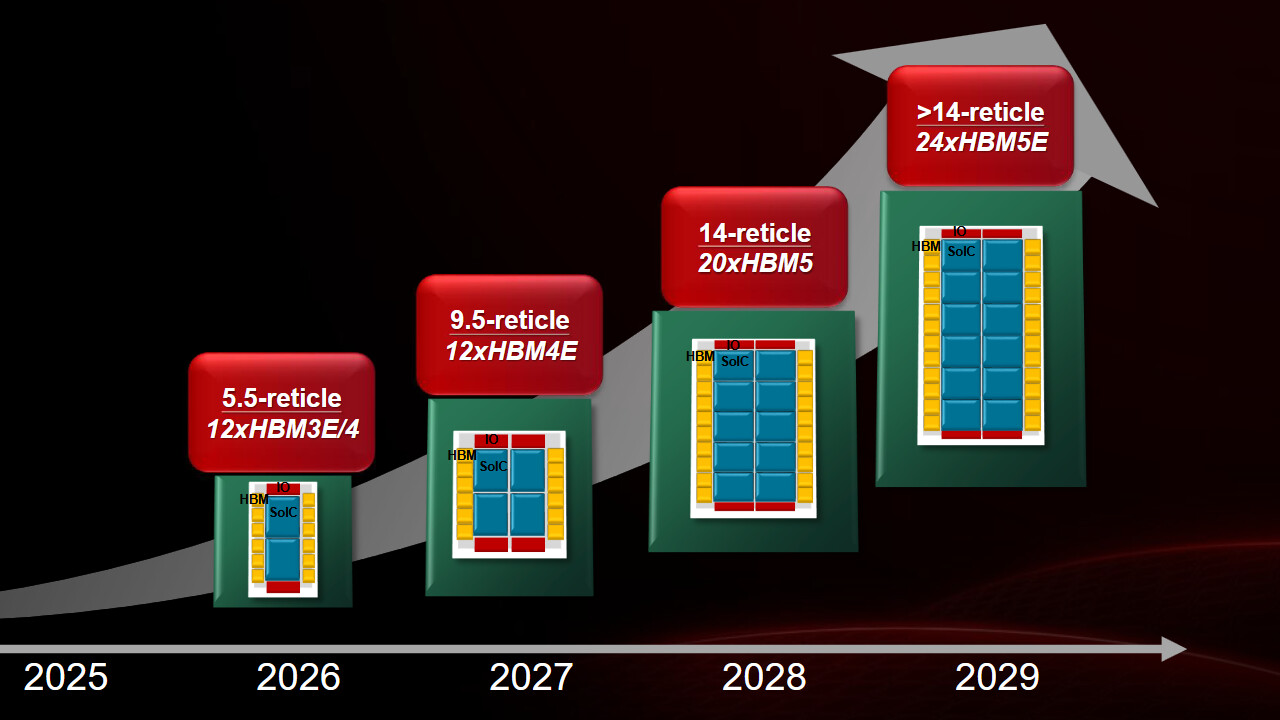

Mega-GPUs für Nvidia, AMD & Co: TSMC zeigt CoWoS-Package mit >11.600 mm² & 24 × HBM5E

TSMC hat CoWoS als den Standard für das Packaging der kommenden Jahre zum „Technology Symposium“ erneut massiv erweitert. Riesige Chips werden daraus resultieren, vom aktuellen Stand mit einer Größe von ungefähr 5,5 Reticles mit 12 × HBM4 können dann Produkte wachsen, die die Größe von über 14 Reticles mit 24 × HBM5E einnehmen.

CoWoS wächst und gedeiht

Seit 2021 bereits in Produktion, hat sich CoWoS (Chips on Wafer on Substrate) zum Kassenschlager entwickelt. Kein moderner größerer Chip ist ohne diese Technologie verfügbar. In diesem Jahr werden so primär gepackte Chips in der Größe von 5,5 Reticles gefertigt, laut TSMC mit einer Yield-Rate (Ausbeute) von über 98 Prozent. Als Reticle-Size-Limit in der Branche gilt die Maximalgröße eines einzelnen Chips, der mit gängigen (EUV-)Belichtungsmaschinen Kantenlängen von bis zu 26 × 33 mm beziehungsweise 858 mm² haben kann. TSMC nutzt als Berechnungsgrundlage vereinfacht in der Regel 830 mm² als Maximum.

Hatte TSMC im letzten Jahr an gleicher Stelle beim Technology Symposium die Grenze auf 9,5 Reticles verschoben, wird sie in diesem Jahr noch einmal deutlich weiter nach oben gesetzt. Nicht nur werden Größen von 14 Reticles bereits ab 2028 anvisiert, im Jahr darauf soll das ganze Konstrukt noch einmal größer werden können. Ohne exakte Angaben steht hier deshalb ein wenig als Platzhalter nur „>14 Reticles“, Platz für 20 Prozent mehr Speicher gegenüber dem vorangegangenen Maximalausbau ist aber ebenso gegeben.

Umgerechnet sind das über 11.600 mm² Fläche nur für die Chips, das 9,5x große CoWoS-Verfahren brachte es auf 7.900 mm². Der darunter liegende Interposer ist noch größer, TSMC bestätigte ihn letztes Jahr mit bis zu 18.000 mm² für das 9,5x große Reticle, bei >14x dürfte wohl eine nochmals deutlich größere Fläche in Beschlag genommen werden.

SoW-X für 40 Reticles und 64 × HBM

Über all dem wird weiterhin „System on Wafer“ (SoW-X) stehen. Bekanntestes Beispiel dafür sind die aktuellen Wafer-Scale-Produkte von Cerebras. Die Weiterentwicklung dieser Variante wird ab 2029 HBM und Logic direkt auf dem Wafer vereinen können. Und dass die Lösungen dann die Größe von über 40 Reticles erreichen, ist für 2029 ebenso geplant.

Intel Foundry vs. TSMC: Meins ist größer als deins!

TSMC begegnet mit der überraschend aggressiven Roadmap auch zuletzt aufkommenden Gerüchten, Intel könnte die Kundschaft streitig machen. Intel Foundry hatte im letzten Jahr nämlich ein Package gezeigt, welches mit bis zu 12 Reticles bereits größer war, als das, was TSMC bis dato geplant hatte. Intel legte daraufhin im März dieses Jahres nach und bestätigte die Produktionsbereitschaft ab dem Jahr 2028. Der Gegenschlag von TSMC ist deshalb heute umfassend ausgefallen.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

- TSMC Technology Symposium 2026

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

-

Künstliche Intelligenzvor 2 Monaten

Top 10: Die beste kabellose Überwachungskamera im Test – Akku, WLAN, LTE & Solar

-

Social Mediavor 2 Monaten

Social Mediavor 2 MonatenCommunity Management und Zielgruppen-Analyse: Die besten Insights aus Blog und Podcast

-

Social Mediavor 2 Monaten

Social Mediavor 2 MonatenCommunity Management zwischen Reichweite und Verantwortung

-

UX/UI & Webdesignvor 3 Monaten

UX/UI & Webdesignvor 3 MonatenEindrucksvolle neue Identity für White Ribbon › PAGE online

-

Entwicklung & Codevor 1 Monat

Entwicklung & Codevor 1 MonatCommunity-Protest erfolgreich: Galera bleibt Open Source in MariaDB

-

Künstliche Intelligenzvor 2 Monaten

Künstliche Intelligenzvor 2 MonatenSmartphone‑Teleaufsätze im Praxistest: Was die Technik kann – und was nicht

-

Apps & Mobile Entwicklungvor 2 Monaten

Apps & Mobile Entwicklungvor 2 MonatenIntel Nova Lake aus N2P-Fertigung: 8P+16E-Kerne samt 144 MB L3-Cache werden ~150 mm² groß

-

Social Mediavor 1 Monat

Social Mediavor 1 MonatVon Kennzeichnung bis Plattformpflichten: Was die EU-Regeln für Influencer Marketing bedeuten – Katy Link im AllSocial Interview