Apps & Mobile Entwicklung

Samsung-Galaxy-Watch-Nutzer sollten dieses Update sofort installieren

Eure Galaxy Watch braucht ein Update. Samsung behebt kritische Sicherheitslücken und optimiert die Leistung der gesamten Galaxy-Watch-Serie. Hier erfahrt Ihr, warum Ihr die Installation nicht aufschieben solltet.

Samsungs Smartwatches gehören zu den Geräten, die regelmäßig Software-Updates erhalten. Obwohl sie weniger häufig sind als die für ihre Smartphone-Pendants, schafft es das Unternehmen immer, durchdachte Verbesserungen in jede neue Version zu packen. Die aktuelle Februar-Firmware wird jetzt auf die Galaxy Watch ausgerollt. Sie bringt dabei nicht nur Qualitätsverbesserungen, es ist auch aus Sicherheitsgründen ein dringendes Update, das Ihr sofort installieren sollte

Welche Galaxy Watches erhalten das Update?

Viele Galaxy-Watch-Nutzer berichten, dass sie die neueste Firmware als Sicherheitsupdate für Februar erhalten haben. Das Update erschien offenbar zuerst für die Galaxy Watch 7 in der vergangenen Woche, bevor es auf weitere Modelle ausgeweitet wurde. Darunter die Galaxy Watch Ultra, die Watch 8 (Testbericht), die Watch 6 und die Watch-5-Serie. Allerdings wird die Version noch schrittweise ausgerollt, so dass sie in einigen Regionen erst in den kommenden Tagen erscheinen wird.

Überraschenderweise ist das Update recht umfangreich, auch wenn es sich nicht um eine größere One-UI-Watch-Version handelt. Auf der Galaxy Watch 8 und Watch 8 Classic ist die Firmware etwa 424 MB groß und trägt die Bezeichnung L330XXU2AZB1/L330OXM2AZB1.

Das zugehörige Changelog hebt Optimierungen und verbesserte Sicherheit hervor. Obwohl die Details spärlich sind, sollte dieses Update zahlreiche Fehler beheben, mit denen die Nutzer konfrontiert sind, einschließlich der Batterieprobleme, die viele in früheren Firmware-Builds bemerkt haben. Auf Reddit haben mehrere Nutzer bereits erwähnt, dass sich die Akkulaufzeit ihrer Galaxy Watch nach dem Update deutlich verbessert hat. Unklar ist allerdings, ob der Patch auch Performance-Probleme in bestimmten Apps behebt, etwa in der Wetter-App.

Warum Ihr mit der Installation nicht warten solltet

Darüber hinaus enthält das Sicherheitsupdate den neuesten Patch vom 5. Februar 2026. Samsung hat zwar keine vollständige Liste der behobenen Schwachstellen zur Verfügung gestellt, aber auf der Grundlage des gleichen Patches, der im letzten Monat an Telefone ausgeliefert wurde, werden wahrscheinlich mehrere Sicherheitslücken behoben, darunter kritische und hochgefährliche Schwachstellen.

Die von Samsung bereitgestellten Korrekturen betreffen Fehler in der biometrischen Authentifizierung und Schwachstellen in bestimmten Apps, die von Angreifern oder Betrügern ausgenutzt werden könnten. Aufgrund dieser Sicherheitsverbesserungen weist das Update darauf hin, dass ein Rollback oder Downgrade auf eine frühere Version nicht mehr möglich sein wird.

Das nächste große Update von Samsung kommt mit One UI 8.5 Watch. Obwohl noch kein offizielles Veröffentlichungsdatum bekannt gegeben wurde, wird erwartet, dass es kurz nach der Veröffentlichung von One UI 8.5 für Samsung Galaxy Telefone und Tablets erscheint.

Welche Samsung Galaxy Watch nutzt Ihr? Habt Ihr das neueste Februar-Update schon erhalten? Sagt es uns in den Kommentaren!

Apps & Mobile Entwicklung

Turtle Beach MC7: Jetzt bekommt auch die Maus ein Touchscreen-Display

Brauchen Mäuse ein Touchscreen-Display? Turtle Beach sagt mit der neuen Command Series MC7 „Ja“. Es dient als Anzeige und Tastenfeld zur Konfiguration der Maus. Übliche Gaming-Features bringt der Luxus-Nager obendrein mit.

Das auffälligste Feature der MC7 fällt sofort ins Auge. An der linken Seite sitzt ein 2,25″-Touchscreen, der laut Turtle Beach die Abtastrate und OBS Studio steuert, Apps öffnet und zur Aktivierung von Makros als Ersatz-Tastenfeld genutzt werden kann, „ohne den Fokus zu verlieren“, schreibt Turtle Beach. Diese Aussage erscheint bei einem Bildschirm ohne klar abgegrenzte Tasten im Spielgeschehen allerdings zunächst einmal unlogisch. Darüber hinaus soll das Display Daten aus Spielen und Systeminformationen anzeigen können.

Wechsel-Akku als Feature

Die Sensorik der MC7 stammt aus dem Turtle-Beach-Portfolio. Eingesetzt wird ein Owl-Eye-Sensor mit einer Abtastrate zwischen 50 und maximal 30.000 dpi und 750 IPS. Die Polling-Rate liegt auch im kabellosen Betrieb über einen mitgelieferten Dongle bei 8.000 Hz. Alternativ kann die MC7 per Bluetooth oder Kabel verbunden werden. Für die beiden primären Maustasten kommen Titan-Taster mit optischer Signalerfassung zum Einsatz. Sie sollen 150 Millionen Klicks überstehen.

Zur Laufzeit macht Turtle Beach keine Angaben. Stattdessen verweist das Unternehmen auf eine praktisch unbegrenzte Laufzeit, die durch einen auswechselbaren Akku erreicht werden soll. Eine Ladestation wird mitgeliefert, es soll sich um das selbe Modell des Headsets Stealth Pro II handeln. Der Akku selbst ist allerdings ein proprietäres Modell. Das heißt auch: Die Maus ist kein Leichtgewicht, sie bringt 135 Gramm auf die Waage.

Das Display beeinflusst zudem die Form des 128 mm × 85 mm × 46 mm großen Mauskörpers, der bei der MC7 kantiger als üblich wirkt. Darin verbaut Turtle Beach insgesamt vier Zusatztasten. Drei werden rund um die Daumenauflange an der linken Seite angeordnet, eine sitzt unter dem 4D-Scrollrad. Das adaptive Rad scrollt bei langsamen Betrieb gerastert und wechselt ähnlich Logitech-Mäusen bei schneller Betätigung automatisch in einen Freilauf. Tasten und Rad können in fünf Profilen per Software konfiguriert werden. Sie regelt auch die RGB-Beleuchtung.

Preis, Verfügbarkeit, kleinere Modelle

Derzeit kann die MC7 lediglich im Webshop von Turtle Beach für rund 160 Euro vorbestellt werden. Die Auslieferung soll ab dem 19. Juli erfolgen. Zu diesem Zeitpunkt sind zudem die 120 Euro teure MC5, die den Touchscreen durch ein seitliches Mausrad ersetzt und sich den Wechselakku spart, und die kabelgebundene MC3 für knapp 80 Euro erhältlich.

Apps & Mobile Entwicklung

TSMC COUPE: Silicon Photonics im Substrat/Interposer setzt Konkurrenz zu

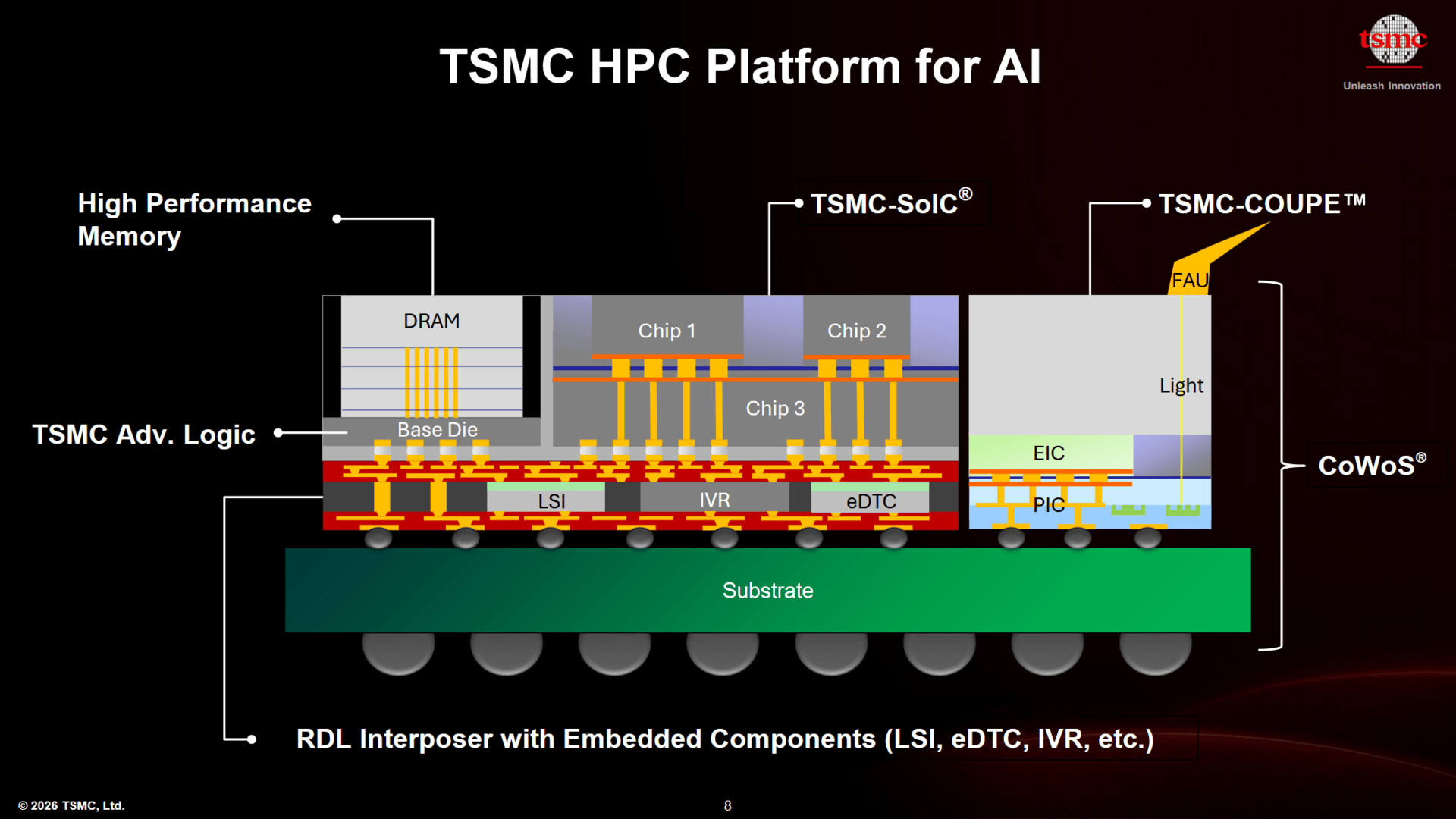

Eine größere Baustelle bei TSMC ist Silicon Photonics. Hier gibt es vielfältige Anbieter, die man mit kompletter Integration toppen will. Vor allem die Thematik rund um Co-Packaged Optics (CPO) hat das Unternehmen auf dem Schirm und könnte mit kompletter Integration via COUPE die Mitbewerber übertreffen.

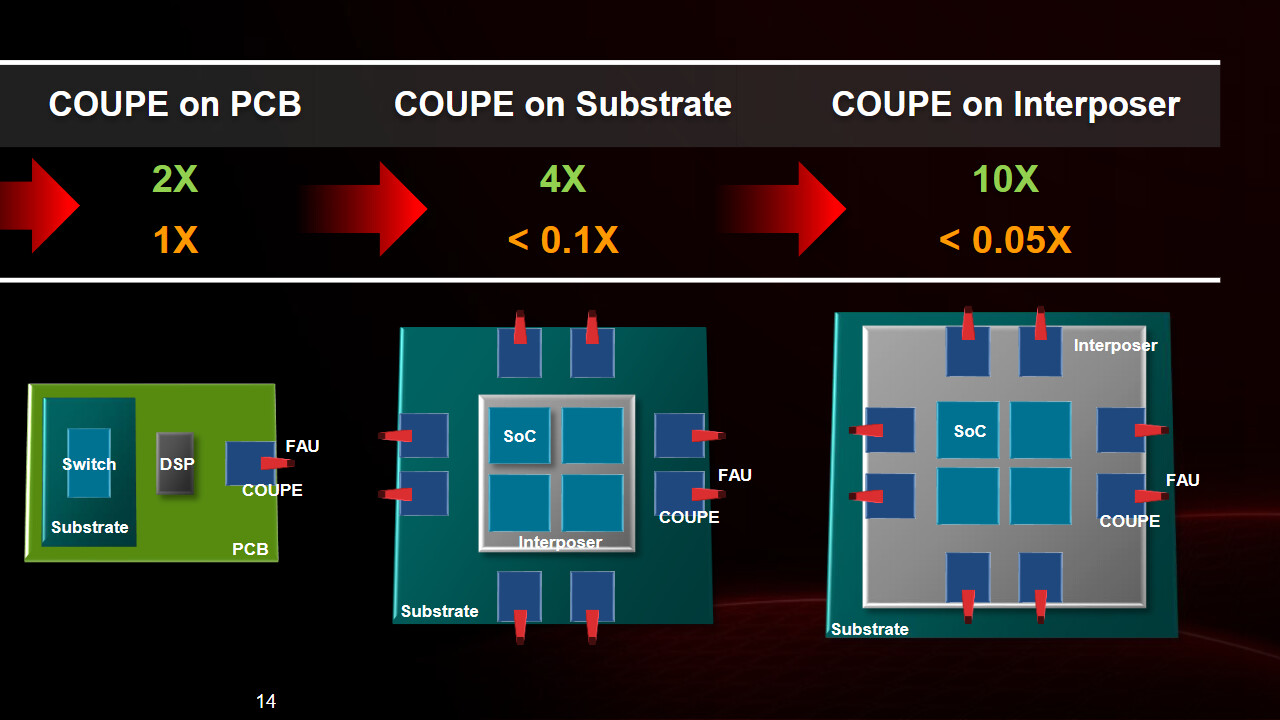

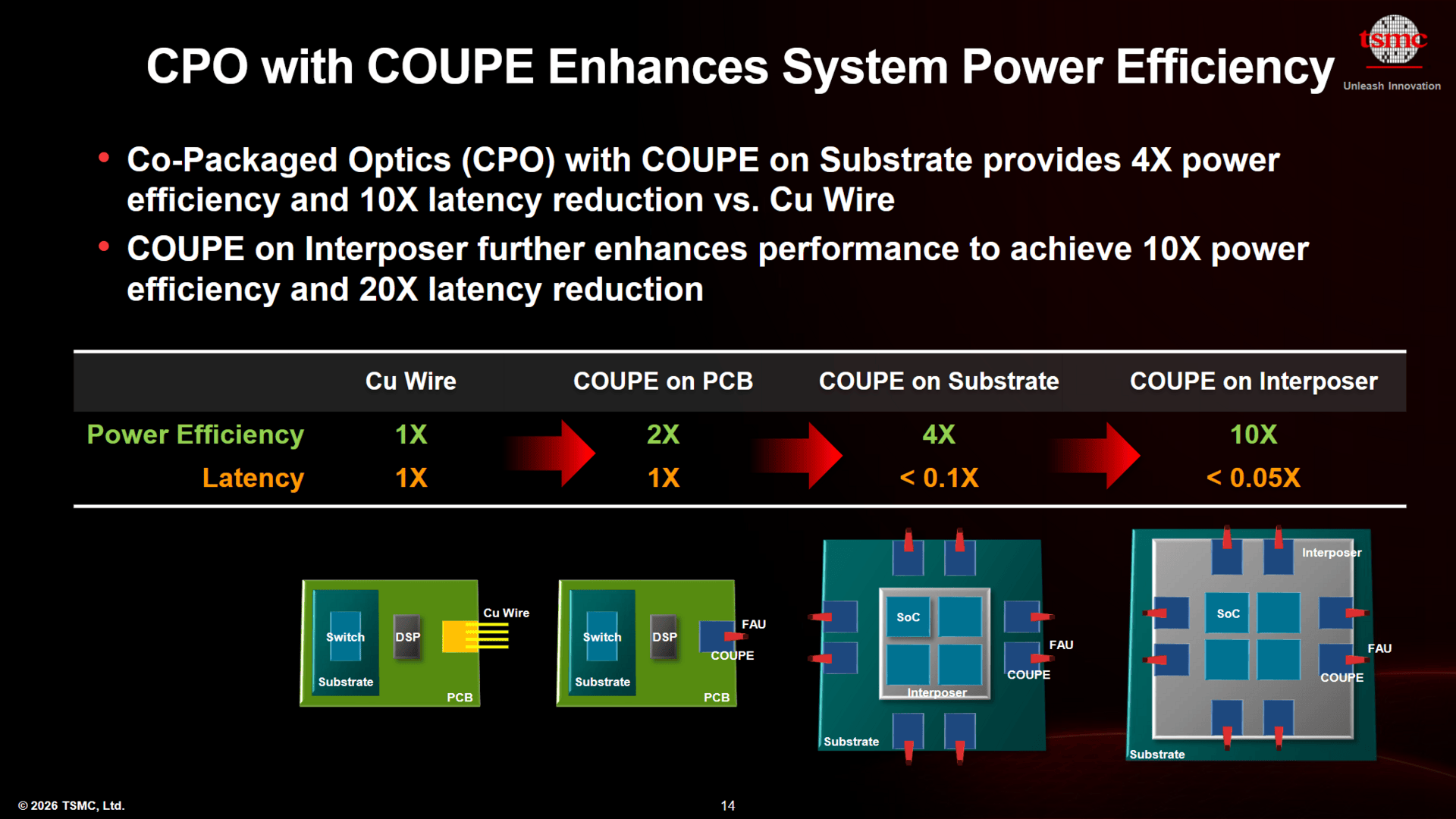

COUPE steht bei TSMC für Compact Universal Photonic Engine. Das Ziel ist es, ein echtes Co-Packaged-Optics-Paket zu schnüren und keine halben Lösungen, die es auf dem Weg dorthin aber definitiv geben wird. Denn in kleinen Schritten geht es bei CPO bisher voran, von der komplett losgelösten Lösung mit optischen Verbindungen im gleichen System, angeschlossen aber noch über ein Kupferkabel, über Silicon Photonics auf dem gleichen PCB, dann dem Substrat und Package bis schließlich zum Finale direkt im Interposer.

Die vom Konzern genannten Boni insbesondere für die komplette Integration am Ende, die laut eigener Aussage nur TSMC umsetzen könne, sind durchaus gewaltig. Die Latenzen sollen bereits bei der Lösung direkt im Substrat effektiv um den Faktor 10 gegenüber einer aktuellen Version „mit Kabel zum Board“ reduziert und die Effizienz verdoppelt werden. Die Basis dafür ist ein 200Gbps micro-ring modulator (MRM), die Serienproduktion hierfür beginnt im zweiten Halbjahr, erklärte TSMC auf Nachfrage. In der nächsten Generation direkt im Interposer sollen die weiteren Vorteile riesig ausfallen, sowohl beim Thema Latenz als auch bei der Effizienz.

TSMC war eher spät dran, was die gesamte Thematik angeht, und startete 2021 auf kleinem Niveau. Aber durch die fortschrittlichsten Technologien dürfte das Unternehmen in den kommenden Jahren den Mitbewerbern durchaus den Rang ablaufen. Erste ehemalige Partner bei Globalfoundries wie Ayar Labs sind nach zwei Generation zu TSMC gewechselt. Voran geht aber einmal mehr Nvidia, die groß auf COUPE schwenken werden. Die allererste Generation bei Nvidia kommt jedoch wohl nur zum Teil von TSMC, SPIL übernimmt hier Restarbeiten. Ähnlich ist es bei Broadcom, auch sie werden von SPIL zu TSMC wechseln.

AMD nutzt die Enosemi-Globalfoundries-Connection

Medial machte zuletzt die Rückkehr von AMD zu Globalfoundries die Runde, um Chips für Silicon Photonics zu beziehen. Was als Neuheit verkauft wurde, entspricht aber nur der halben Wahrheit. Denn im letzten Jahr hatte AMD das Unternehmen Enosemi übernommen, das wiederum Silicon-Photonics-Produkte auf Basis von Globalfoundries‘ IP entwickelt hat bei Globalfoundries ließ. Entsprechend kommen nun auch die darauf basierenden Lösungen von AMD von Globalfoundries.

Wie lange das so bleiben wird, ist jedoch abzuwarten. Da die Riesen Broadcom und Nvidia zu TSMC COUPE wechseln, könnte dies auch bei AMD in Zukunft der Fall sein. Denn vor allem des Gesamtpaket bei TSMC, fast alles aus einer Hand zu bekommen, dürfte neben den besten Fertigungstechnologien durchaus eine Rolle spielen.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

- TSMC Technology Symposium 2026

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

Apps & Mobile Entwicklung

TSMC A13/A12-Fertigungsprozess: „1,2 nm“ mit Super Power Rail (ohne High-NA-EUV) ab 2029

Mit den Fertigungsprozessen A13 und A12 geht TSMC in die nächste Dekade. Kombiniert mit Super Power Rail wird A12 die Flaggschiffserie. Realisiert werden soll das alles weiterhin ohne High-NA-EUV, wie TSMC auf Rückfrage verdeutlicht. Die modernsten Low-NA-EUV-Belichter geben das alles problemlos her, erklärt der Hersteller.

Dr. Kevin Zhang, Senior Vice President und Deputy Co-COO bei TSMC (und zuvor auch mal 12 Jahre bei Intel), erläuterte am Vorabend des Symposiums in den USA gegenüber der Presse die kommenden Entwicklungsschritte – mit extrem hohem technischen Verständnis. Auf dem Papier sieht es dabei so aus, als würden die Schritte kleiner werden. Dies ist aber der Zweigleisigkeit geschuldet, die TSMC derzeit fährt: Es gibt einen Standardprozess, und dann eine Linie, die auf BSPD, also die rückseitige Stromversorgung der Chips setzt.

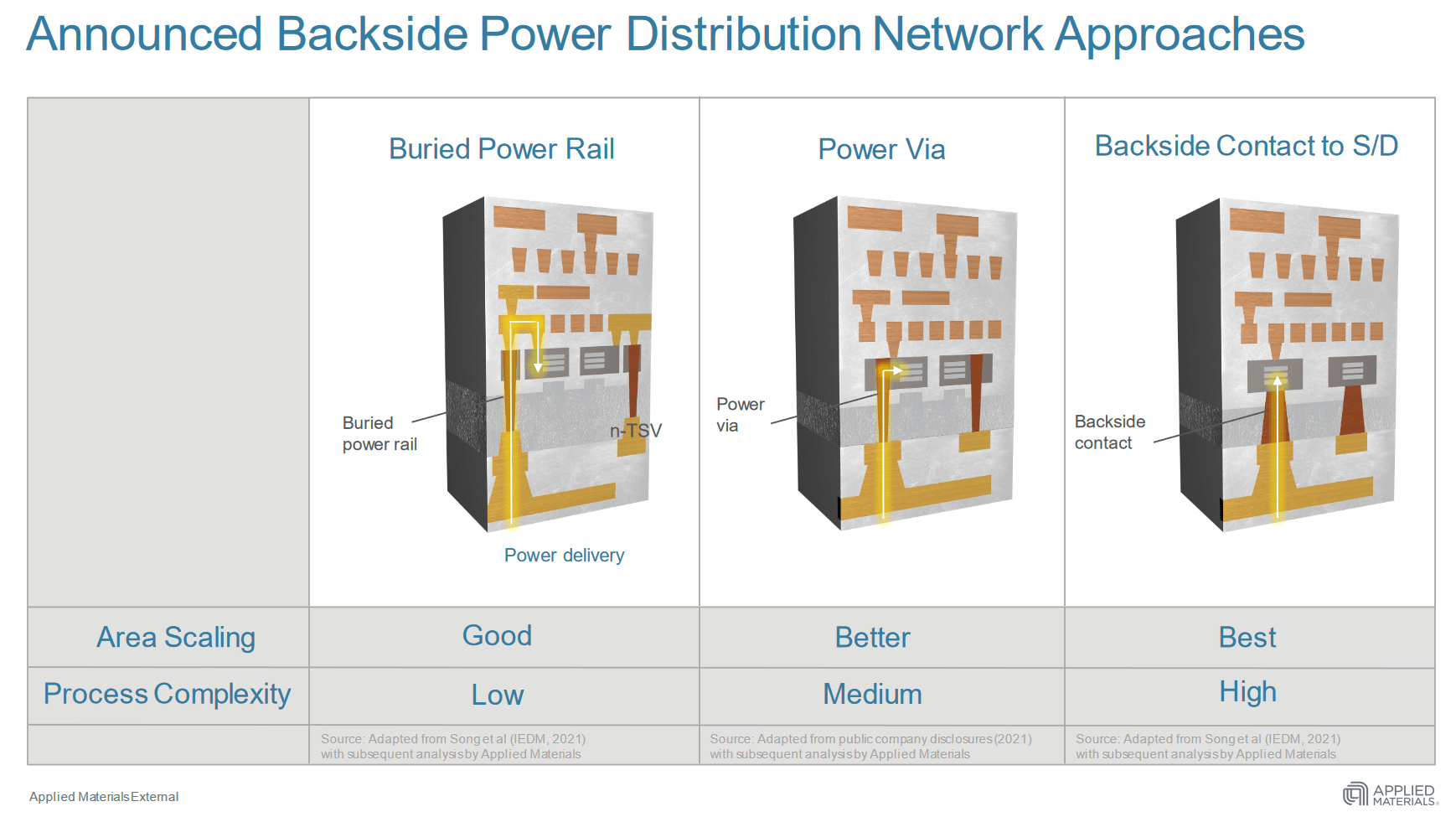

Diese Zweigleisigkeit wird aktuell beim N2-Prozess eingeführt. Denn der kommende Fertigungsschritt A16 ist eigentlich N2 im Herzen, jedoch mit Backside Power Delivery (BSPN) ausgestattet. Der Nachfolger von N2 ohne BSPD wird der A14-Prozess, der Nachfolger von A16 mit BSPD letztlich deshalb A12. Die Basis dafür ist entsprechend der A14-Prozess mit Optimierungen. Auch hier setzt TSMC auf das sogenannte Super Power Rail (SPR), der besten Adaption von BSPD mit direktem rückseitigem Kontakt (die ganz rechte Lösung im Bild). Intel nutzt seit Panther Lake in Intel 18A die mittlere Variante mit Power VIAs.

A14-Prozess bekommt Shrink auf A13

Auf den A14-Prozess folgt im Standardverfahren binnen eines Jahres der A13-Prozess. Dies wiederum ist heutzutage vergleichbar mit dem Schritt von N3E auf N3P oder zukünftig N2 auf N2P. Mit einem optischen Shrink kann etwas Fläche von rund sechs Prozent eingespart werden, hier und da gibt es zudem minimale Vorteile durch den zeitlichen Versatz des Prozesses, sodass zusätzliche design-technology co-optimizations (DTCO) greifen und eine verbesserte Leistung und Effizienz versprechen. Da die Design-Tools und –Regeln identisch bleiben, können A14-Kunden schnell und direkt auf den angepassten Prozess schwenken.

High-NA-EUV bei TSMC weiterhin kein Thema

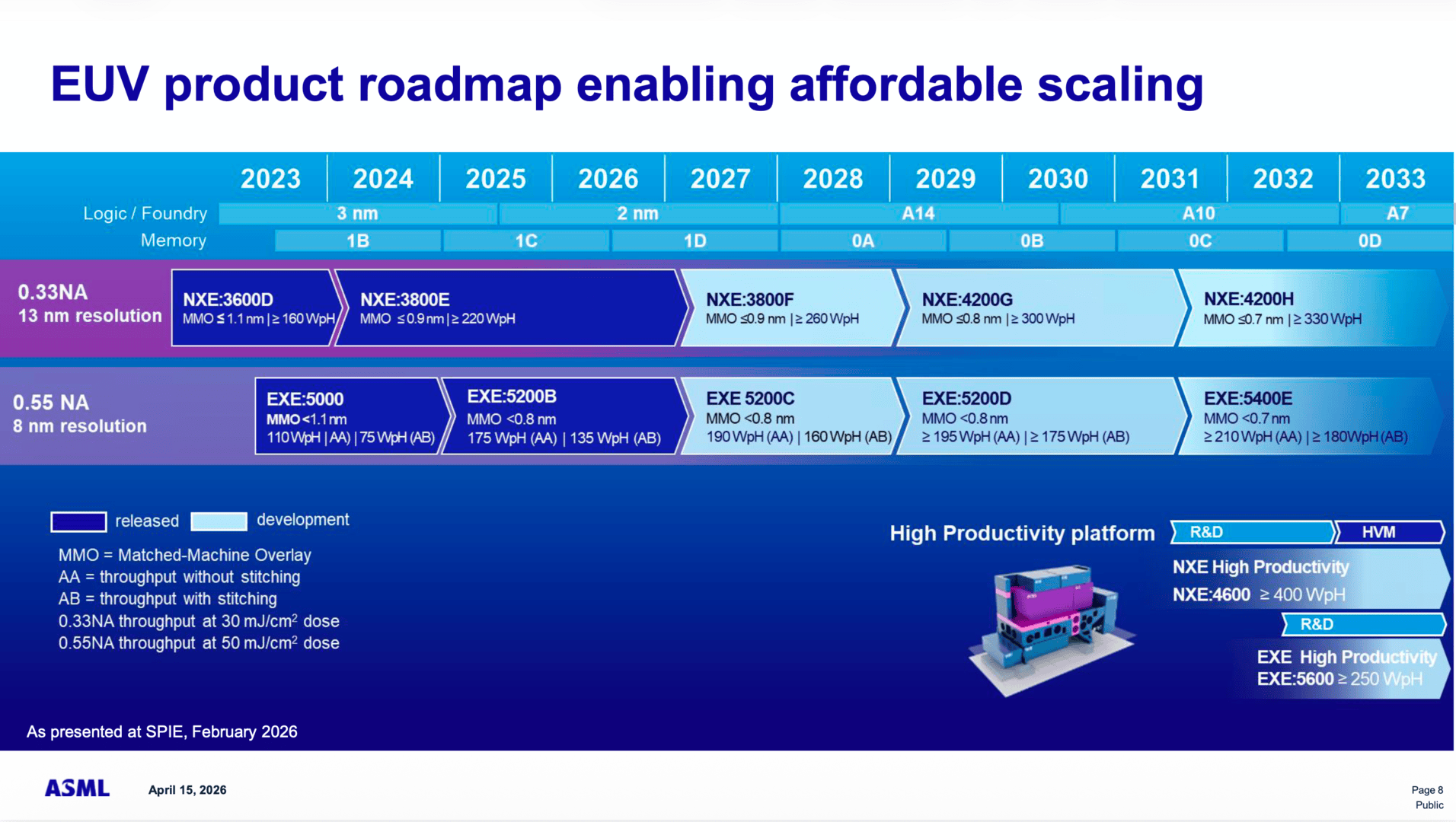

Stolz erklärte Zhang, dass TSMC auch bei den Prozessen für das Jahr 2029 auf High-NA werde verzichten können. Bisher hat das Unternehmen stets eine Möglichkeit gefunden, es wirtschaftlich mit den bestehenden Belichtern zu realisieren – auch heute monierte TSMC den sehr hohen Preis des rund 400 Millionen Euro teuren Systems. Die Entscheidung, wann High-NA bei TSMC zum Einsatz kommt, ist damit erneut vertagt worden, nachdem es im letzten Jahr bereits hieß, dass es vor 2029 nicht gebraucht wird.

Bei Intel könnten die ersten High-NA-Systeme eventuell ab 2027/2028 in der Produktion genutzt werden, aber auch hier klang es zuletzt danach, dass es eher später als früher wird. Ab dem Jahr 2030 dürften die High-NA-EUV-Systeme zudem einen deutlich höheren Reifegrad erreicht haben und so bestehende Low-NA-EUV-Systeme besser ergänzen können. Vermutlich tendiert TSMC erst dann zu einer Integration.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

- TSMC Technology Symposium 2026

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

-

Künstliche Intelligenzvor 2 Monaten

Top 10: Die beste kabellose Überwachungskamera im Test – Akku, WLAN, LTE & Solar

-

Social Mediavor 2 Monaten

Social Mediavor 2 MonatenCommunity Management und Zielgruppen-Analyse: Die besten Insights aus Blog und Podcast

-

Social Mediavor 2 Monaten

Social Mediavor 2 MonatenCommunity Management zwischen Reichweite und Verantwortung

-

UX/UI & Webdesignvor 3 Monaten

UX/UI & Webdesignvor 3 MonatenEindrucksvolle neue Identity für White Ribbon › PAGE online

-

Entwicklung & Codevor 1 Monat

Entwicklung & Codevor 1 MonatCommunity-Protest erfolgreich: Galera bleibt Open Source in MariaDB

-

Künstliche Intelligenzvor 2 Monaten

Künstliche Intelligenzvor 2 MonatenSmartphone‑Teleaufsätze im Praxistest: Was die Technik kann – und was nicht

-

Apps & Mobile Entwicklungvor 2 Monaten

Apps & Mobile Entwicklungvor 2 MonatenIntel Nova Lake aus N2P-Fertigung: 8P+16E-Kerne samt 144 MB L3-Cache werden ~150 mm² groß

-

Social Mediavor 1 Monat

Social Mediavor 1 MonatVon Kennzeichnung bis Plattformpflichten: Was die EU-Regeln für Influencer Marketing bedeuten – Katy Link im AllSocial Interview